AR# 55660

|Vivado Constraints - How to resolve DRC Warning:[DRC 23-20] Rule violation (CFGBVS-1) Neither the CFGBVS nor CONFIG_VOLTAGE voltage property is set in the current_design

描述

Vivado 2013.1 has started returning DRC warnings for my design.

Why does Vivado need the CFGBVS and CONFIG_VOLTAGE properties set in XDC and what values should be set for the two?

The following is from the Error Message:

set_property CFGBVS value1 [current_design]

#where value1 is either VCCO or GND

set_property CONFIG_VOLTAGE value2 [current_design]

#where value2 is the voltage provided to configuration bank 0

Refer to the device configuration user guide for more information.

解决方案

Incorrect voltage supply for the configuration interfaces on board can result in configuration failure or device damage.

The Vivado DRC tool can check if the configuration interfaces of the device have correct voltage support based on the Configuration Bank Voltage Select (CFGBVS), CONFIG_VOLTAGE, and the CONFIG_MODE properties settings.

Those properties are also needed to support some other features in I/O Planning, such as generating an IBIS Model or CSV file.

Those properties tell Vivado how the device configuration interfaces are used and connected on board. For example, the CFGBVS property reflects how the CFGBVS pin is connected.

If you do not set those properties for the design, Vivado will not perform the related DRC checks. Then the designer has to make sure that the device has the correct voltage support for configuration interfaces on board.

As suggested in the DRC message, the CFGBVS and CONFIG_VOLTAGE properties can be set in either of the two ways below.

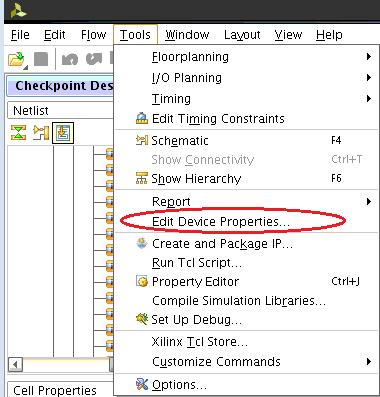

1) Open Synthesized Design and Use the 'Edit Device Properties' function in the 'Tools' menu.

Select correct values for the two properties and click "OK".

Then click the "Save Constraints" button to save them to XDC file.

2) Add constraints in the XDC file directly

This DRC message has provided the XDC syntax examples of the CFGBVS and CONFIG_VOLTAGE properties:

set_property CFGBVS value1 [current_design]

#where value1 is either VCCO or GND

set_property CONFIG_VOLTAGE value2 [current_design]

#where value2 is the voltage provided to configuration bank 0

Note:

In GUI project mode, when you receive this warning in bitstream generation, setting the two properties by running the set_property commands in the Tcl Console and then re-running "Generate Bitstream" will NOT resolve the warning.

This is because the properties do not get applied into the Implementation run that had already completed. When you re-run "Generate Bitstream" this Implementation run will be loaded and only the properties stored in it will be used.

To remove the warning, you must do one of the following:

- Set the two properties using "Edit Device Properties" or in the XDC file as mentioned above, then re-run Implementation and bitstream generation.

- Open the Implemented Design or open the routed DCP, set the two properties by running the set_property commands in the Tcl Console, then generate the bitstream by running "write_bitstream" command in the Tcl Console.

- If you do not need Vivado DRC tool to check the configuration voltage support, you can just ignore this warning.

For more information about those properties and the voltage support of configuration interfaces, you can refer to the following documentation:.

- Configuration User Guide for each device family : information about Configuration Mode, Compatible Voltages, and CFGBVS Connection.

UG470 - 7 Series FPGAs Configuration User Guide

http://www.xilinx.com/support/documentation/user_guides/ug470_7Series_Config.pdf

UG570 - UltraScale Architecture Configuration User Guide

http://www.xilinx.com/support/documentation/user_guides/ug570-ultrascale-configuration.pdf

UG912 - Vivado Properties Reference Guide : properties usage and syntax.

http://www.xilinx.com/support/documentation/sw_manuals/xilinx2015_4/ug912-vivado-properties.pdf

UG899 - Vivado I/O and Clock Planning : examples of how Vivado tools use these properties.

http://www.xilinx.com/support/documentation/sw_manuals/xilinx2015_4/ug899-vivado-io-clock-planning.pdf