AR# 58981

|7 Series GTP Transceivers - TX and RX Latency Values

描述

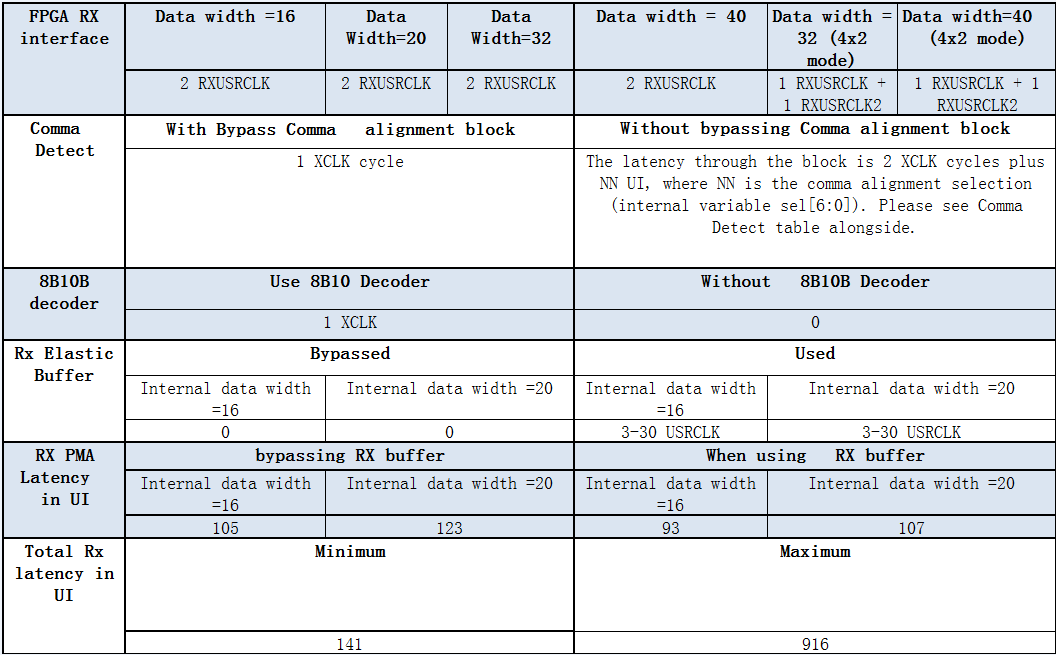

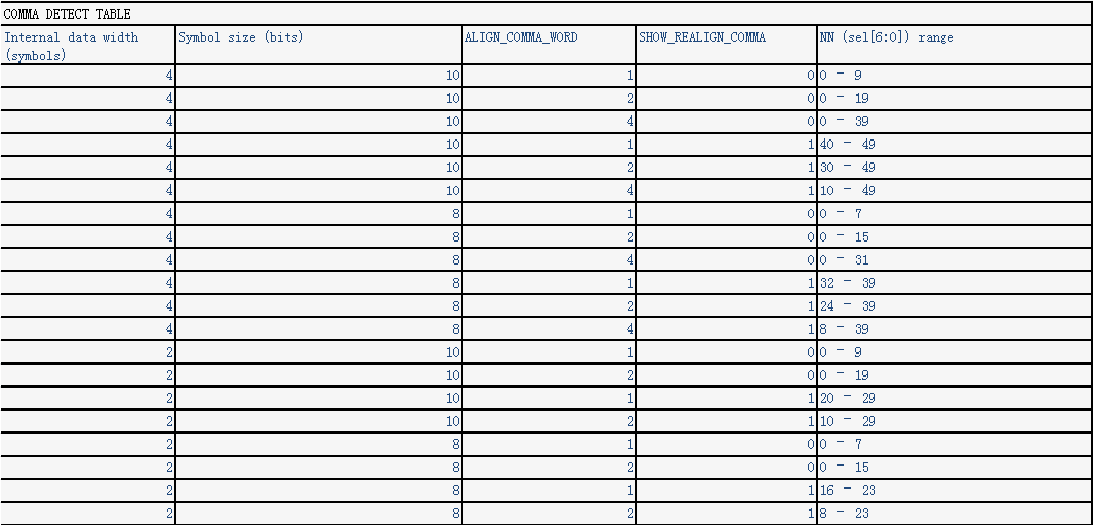

This answer record provides the TX and RX latency values for the 7 series FPGA GTP Transceiver. The tables will be added to the 7 Series FPGAs GTP Transceivers User Guide (UG482).解决方案

Notes:

- RXDDIEN must be 1 to ensure predictable fixed latency when using RX buffer bypass.

- The minimum and maximum are theoretical. These configurations may not map to any protocol.

- USRCLK and USRCLK2 phases are assumed to be matching according to the user guide.

- The latency through the TX fabric interface will depend on one's precise definition of latency; the entries in the above table are accurate if latency is defined as the time from the clock edge that puts data on TXDATA to the clock edge that clocks the first part of that data out of the fabric interface (into the internal PCS), neglecting clock insertion time from the fabric into the GT.

本答复记录是否对您有帮助?