AR# 66715

|2016.1-2017.2 Zynq UltraScale+ MPSoC - QSPI programming on a Zynq UltraScale+ device requires boot in JTAG mode

描述

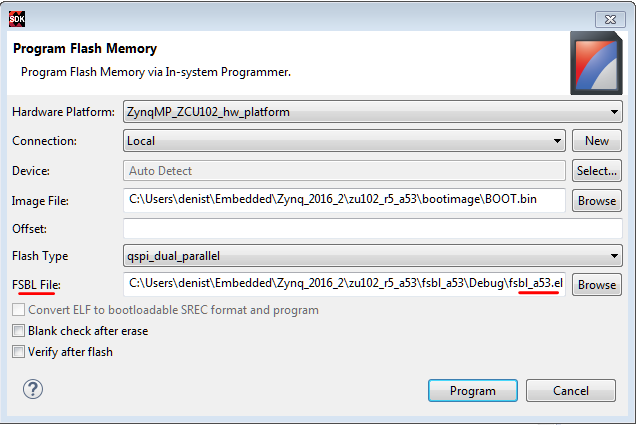

We are programming QSPI flash with a custom board which requires the Zynq UltraScale+ device to boot in JTAG mode from both XSDK and Vivado Hardware Manager.

QSPI programming on a ZCU102 board requires the Zynq UltraScale+ device to boot in JTAG mode from both XSDK and Vivado Hardware Manager.

Note: this Answer record applies to the 2017.2 release as well as earlier versions. Please see below for differences.

解决方案

The programming flow in 2017.2 and earlier is to set the boot mode pins to JTAG and issue a PS_POR_B before programming the QSPI.

This tool limitation will be removed in 2017.3.

=========

The programming flow also requires you to specify an FSBL that runs on A53-0 (64-bit) (an FSBL running on R5-0 will not work) to help the programmer to initialize the system.

If you are QSPI programming with SDK 2017.2 and earlier, the FSBL should be generated for an A53-0 (64-bit) processor only.

For the 2017.3 SDK and later versions, FSBL can run from either an A53-0 (64-bit) or R5-0 processor while QSPI indirect programming:

Note: FSBL for A53-0 (32-bit) is NOT supported.

链接问答记录

主要问答记录

| Answer Number | 问答标题 | 问题版本 | 已解决问题的版本 |

|---|---|---|---|

| 66752 | Zynq UltraScale+ MPSoC ZCU102 评估套件 - 已知问题和发布说明主答复记录 | N/A | N/A |