AR# 67468

|2016.1 - Simulation - XADC simulation model includes unnecessary check for 'DWE' pulse width

描述

When using an XADC core in my design, I am getting unexpected results during simulation.

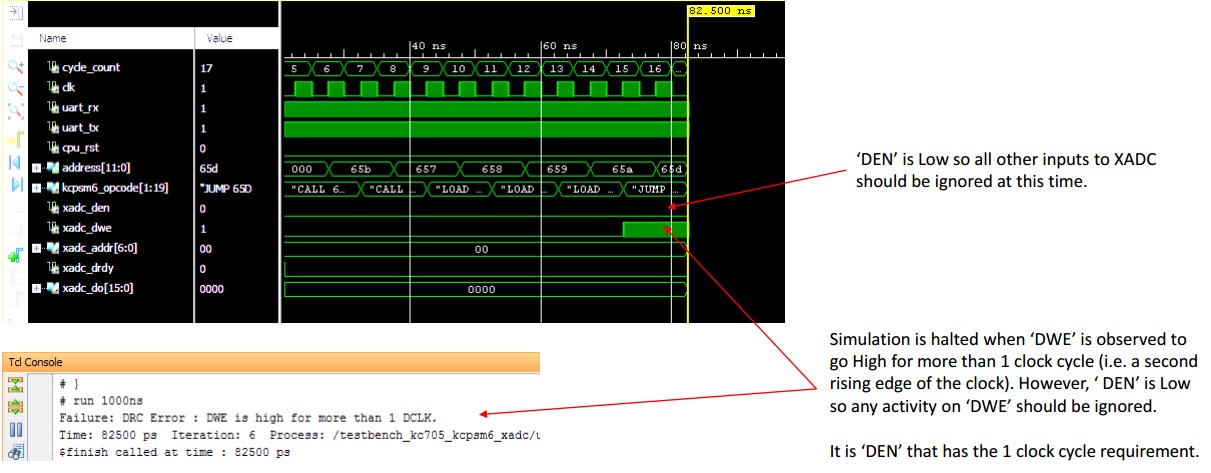

As shown in the following screen capture, it appears that the XADC model is including an unnecessary check for 'DWE' pulse width.

This is causing simulation to stop when 'DWE' is High for more than one clock cycle even when 'DEN' is permanently Low.

All DRP inputs to XADC should be ignored when 'DEN' is Low. The one cycle requirement should only be applied to the 'DEN' input.

解决方案

This issue has been resolved in Vivado 2016.2.

As a work-around, avoid driving DWE high for more than 1 DCLK under this circumstance.

本答复记录是否对您有帮助?

| AR# 67468 | |

|---|---|

| 日期 | 07/05/2016 |

| 状态 | Active |

| Type | 综合文章 |

| Tools | |

| IP | |

People Also Viewed