AR# 71877

|UltraScale+ PCI Express Integrated Block (Vivado 2018.2/2018.3/2019.1/2019.2) - Reconfigurable Stage 2 support for Tandem PCIe w/ Field Updates

描述

Version Found:

- DMA / Bridge Subsystem for PCI Express - (Vivado 2018.2/2018.3/2019.1/2019.2)

- UltraScale+ PCI Express Integrated Block - (Vivado 2018.2/2018.3/2019.1/2019.2)

Version Resolved and other Known Issues: DMA Subsystem for PCI Express (Xilinx Answer 65443) / UltraScale+ PCI Express Integrated Block (Xilinx Answer 65751)

(PG213) The UltraScale+ PCI Express Integrated Block Product Guide mentions "Reconfigurable Stage Twos".

"Essentially with Reconfigurable Stage Twos, stage 2 bitstreams can act as partial bitstreams, and therefore they are interchangeable when paired with a fixed stage 1 bitstream."

In UltraScale devices, there was a restriction that the stage 2 bitstream used to complete the initial configuration must come from the same checkpoint that generated the stage 1 bitstream.

The Product Guide states that this restriction no longer applies in UltraScale+ devices. However, due to an issue that has been detected in Vivado 2018.3 with UltraScale+ devices, "Reconfigurable Stage Twos" are not yet supported in UltraScale+ devices.

This means the requirement which existed for UltraScale device also continues to apply to UltraScale+ devices.

解决方案

For the Tandem PCIe with Field Updates flow with UltraScale+ devices in Vivado 2018.2 through 2019.2, the stage 2 bitstream that is used to complete the initial configuration must come from the same checkpoint that generated the stage 1 bitstream.

Creation of partial bitstreams can be set in the design_field_updates.tcl script as shown below:

Original:

set updateVer1BitstreamsResult [genBitForTandemFieldUpdate $updateVer1Name {TandemPCIe}]

Updated Version:

set updateVer1BitstreamsResult [genBitForTandemFieldUpdate $updateVer1Name {TandemPCIe PR}]

This will generate both tandem stage1 and stage2 files along with PR bitfiles for version 1.

Original:

set updateVer2BitstreamsResult [genBitForTandemFieldUpdate $updateVer2Name {TandemPCIe}]

Updated Version:

set updateVer2BitstreamsResult [genBitForTandemFieldUpdate $updateVer2Name {PR}]

This will generate PR bitfiles for Stage2 and not Tandem Bitfiles for version 2.

These partial bitstreams will reconfigure only the update region, not the XDMA region (if that core is used).

Reconfigurable stage 2 bitstreams include the XDMA part of the IP core, whereas the partial bitstreams for the users dynamic region do not.

Note:

- The above changes are only needed for Vivado 2018.2/2018.3. They have already been applied in Vivado 2019.1.

- In Vivado 2019.1.2 and newer versions, an additional parameter needs to be set for the same functionality as in older versions of Vivado.

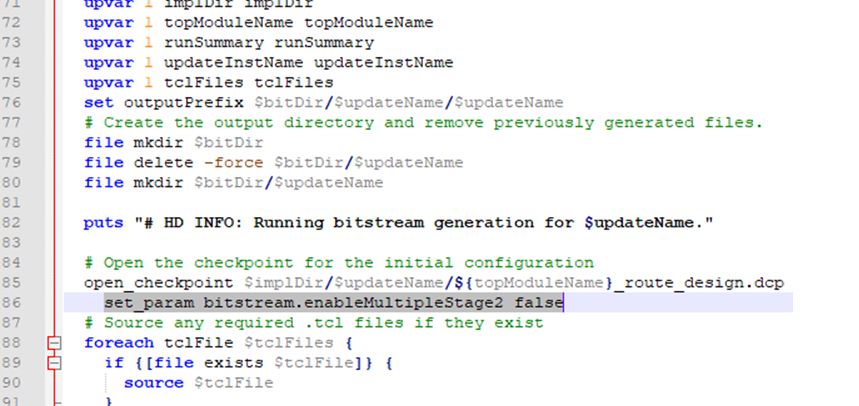

Add "set_param bitstream.enableMultipleStage2 false" in the generate_bistreams.tcl file as shown below.

Revision History:

02/10/2019 - Initial Release

链接问答记录

主要问答记录

| Answer Number | 问答标题 | 问题版本 | 已解决问题的版本 |

|---|---|---|---|

| 65443 | DMA Subsystem for PCI Express - Release Notes and Known Issues for Vivado 2015.3 and newer tool versions | N/A | N/A |

| 65751 | UltraScale+ PCI Express Integrated Block - Release Notes and Known Issue | N/A | N/A |