AR# 73541

|7 系列/Virtex-6 FPGA 设计咨询:破解比特流加密

描述

本设计咨询主要面向 7 系列和 Virtex-6 FPGA,其中包含赛灵思针对 2020 年 4 月 15 日发布的一篇有关破解比特流加密的文章的回应,详情已于“USENIX Security 2020”大会上发表。

此攻击被作者称为“Starbleed”。

如需了解如何注册接收新设计咨询通知的更多信息,请参阅 (赛灵思答复记录 18683)。

解决方案

7 系列 FPGA

作者成功利用了 AES-CBC 模式下缺少误差扩展以及以 WBSTAR 为代表的配置命令实际上可在认证成功前执行的漏洞,使其得以成功突破器件安全屏障。

这项攻击的复杂程度与已证实针对这些器件的著名 DPA 攻击相似,因此并不会造成器件安全态势被弱化。

6 系列 FPGA

作者成功利用了 AES-CBC 模式下缺少误差扩展以及以 WBSTAR 为代表的配置命令实际上可在认证成功前执行的漏洞,

使其得以成功提取大部分明文配置信息,导致恢复后的网表不完整。

这项攻击的复杂程度与已证实针对这些器件的著名 DPA 攻击相似,因此并不会造成器件安全态势被弱化。

Zynq-7000 SoC 器件、UltraScale FPGA、UltraScale+ FPGA、Zynq UltraScale+ MPSoC 器件和 Versal ACAP

当您启用以下安全功能,这些器件可抵御这些类型的攻击:

Zynq-7000 SoC:AES 加密 + RSA-2048 认证

UltraScale 与 UltraScale+ FPGA:- 方法一:AES-GCM 加密/认证 + 配置计数

- 方法二:AES-GCM 加密 + RSA-2048 认证

Zynq UltraScale+ SoC:

- 方法一:通过 RSA-4096 + AES-GCM 加密实现 HWRoT (Hardware Root of Trust) 启动模式

- 方法 二:通过 AES-GCM 加密/认证实现 Encrypt Only 启动模式

Versal ACAP:

- 方法一:通过 RSA-4096/ECDSA-384 认证 + AES-GCM 加密实现 A-HWRoT (Asymmetric Hardware Root of Trust) 启动模式

- 方法二:通过 AES-GCM 加密/认证实现 S-HWRoT (Symmetric Hardware Root of Trust) 启动模式

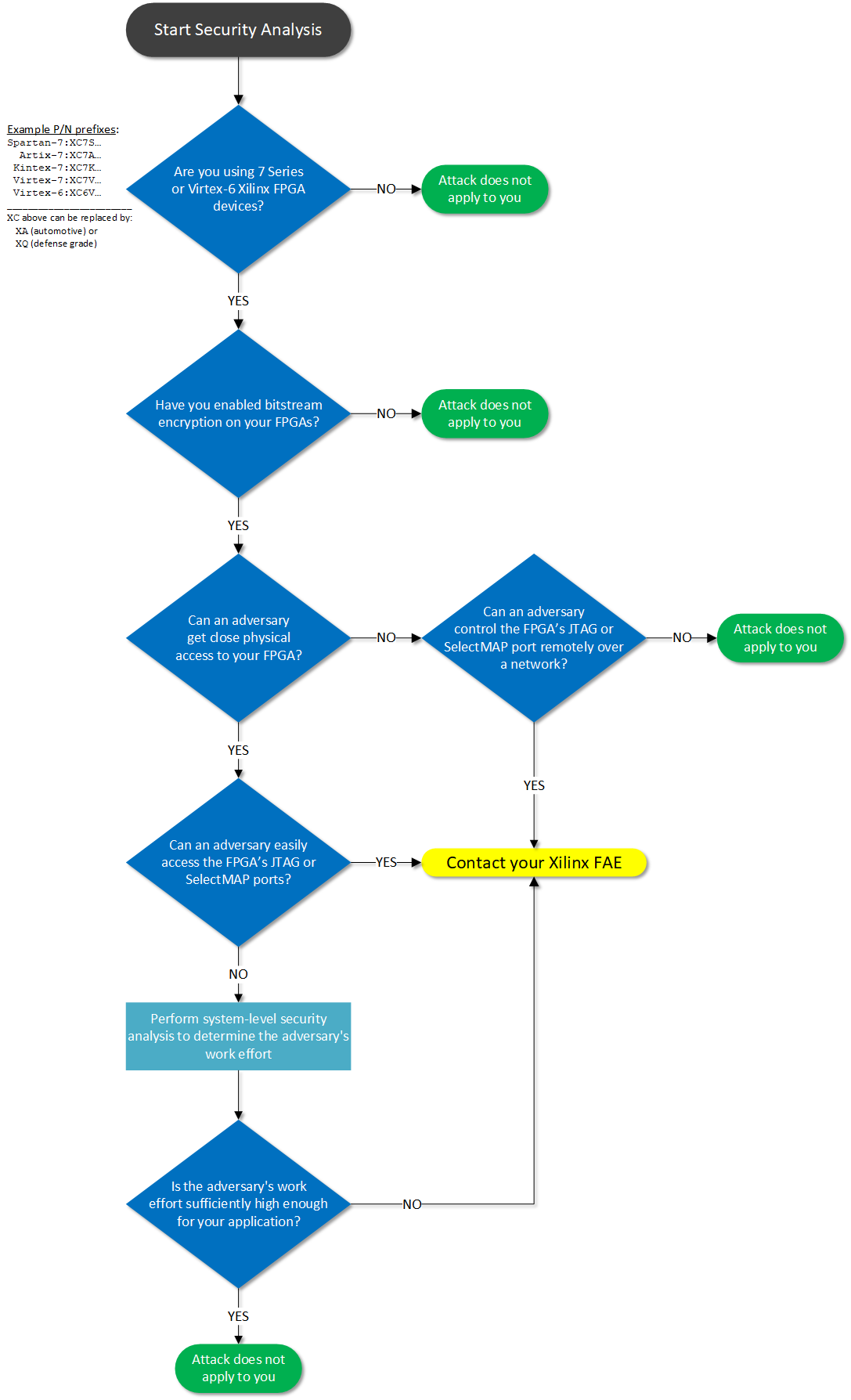

重要的是首先明确这项攻击是否会对现有系统造成影响。

请参阅以下“安全分析流程图”,它可用于判定现有系统是否受到影响。

starbleed_analysis_flowchart.png

如有其它问题,请联系您所在地的赛灵思代表。

本答复记录是否对您有帮助?