产品描述

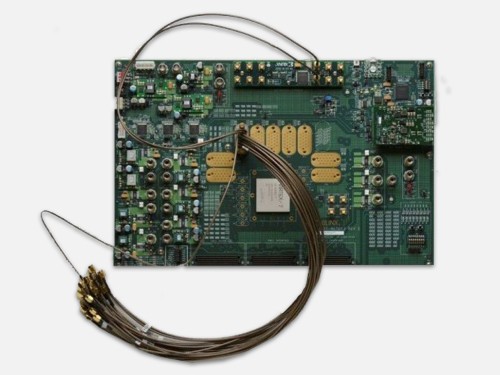

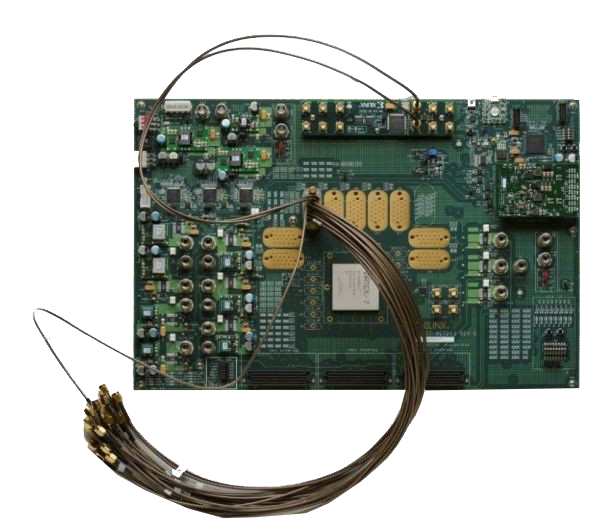

Virtex®-7 FPGA VC7203 特性描述套件为对板上 Virtex-7 V485T FPGA 的 28 GTX (12.5Gbps) 收发器进行特性描述和评估提供了硬件环境。VC7203 可通过 Vivado® 或 ISE® design suite 来评估集成式误码率测试器 (IBERT) 演示。每个 GTX Quad 及其相关参考时钟均从 FPGA 路由至用于连接 Samtec BullsEye 连接器的连接器焊盘。用户可以使用带有 BullsEye 连接器以及 SMA-10 标准连接器的电缆来连接各种评估平台,从背板与光学评估板到高速测试设备不一而足。每个 BullsEye 连接器都会处理一个完整的 GTX Quad、4 个发送/接收对以及 2 个独立的参考时钟,从而可以以最灵活的方式来测试定制应用。

主要性能和优势

- 在 Virtex-7 V485T FPGA 上描述和评估 28 GTX (12.5Gbps) 收发器的硬件环境

- 硬件、设计工具、IP、以及预验证参考设计

- 集成式误码率测试器 (IBERT) 参考设计

- BullsEye 连接头支持完整的 GTX Quad,包含 4 个传输/接收对

- 为 GTH 收发器和参考时钟提供 9 个 Samtec BullsEye 连接器衬垫

- 2对带有 SMA 连接器的差分 MRCC 输入

- System ACE™ SD 控制器

- 扩展 I/O, 包含 3 个 FPGA Mezzanine Card (FMC) 接口

特色 Xilinx 器件

符合 ROHS 规范的 VC7203 套件,包含 XC7VX485T-3FFG1761E FPGA

| 逻辑单元 | 485,760 |

|---|---|

| DSP Slice | 2,800 |

| 内存 (Kb) | 37,080 |

| GTY 12.5 Gb/s 收发器 | 56 |

| I/0 引脚 | 700 |

开发板特性

包含 VC7203 特性描述开发板

通信与网络

- 为 GTH 收发器和参考时钟提供 9 个 Samtec BullsEye 连接器衬垫

- 2对带有 SMA 连接器的差分 MRCC 输入

- USB-UART 桥

时钟技术

- 固定 200MHz 2.5V LVDS 振荡器,与多区域时钟输入引脚相连

- SuperClock-2 模块,支持多种频率

显示

- 电源状态 LED

- 通用 DIP 开关、LED、按钮和测试 I/O

扩展连接器

- 3 x VITA 57.1 FPGA 夹层卡(FMC) 高引脚数 (HPC) 连接器

配置

- Digilent USB JTAG 编程端口

存储器

- System ACE™ SD 控制器

控制 & I/O

- I2C 总线

功耗

- 板上数字电源的 PMBus 连接功能

特色 Xilinx 器件

符合 ROHS 规范的 VC7203 套件,包含 XC7VX485T-3FFG1761E FPGA

| 逻辑单元 | 485,760 |

|---|---|

| DSP Slice | 2,800 |

| 内存 (Kb) | 37,080 |

| GTY 12.5 Gb/s 收发器 | 56 |

| I/0 引脚 | 700 |

内含物件

VC7203 评估板

包含 Virtex-7 XC7VX485T-3FFG1761E FPGA

整套 Vivado® Design Suite: Design Edition

Virtex-7 XC7VX485T FPGA 节点锁定 & 器件锁定,包含 1 年更新及技术支持

Samtec Bullseye 线缆

10 个标准 SMA

SuperClock-2 模块,支持多种频率

标题

日期

设计工具

| 名称 | 说明 | 许可证类型 |

|---|---|---|

| Vivado Design Suite Design Edition | Xilinx Vivado® Design Suite 是一款以 IP 核及系统为中心的设计环境,这一全新构建的环境具有革新意义,能够显著加速 FPGA 和 SoC 系列器件的设计效率。 | Virtex-7 XC7VX485T FPGA 节点锁定 & 器件锁定,包含 1 年更新及技术支持 |

Default

Default

标题

日期