产品描述

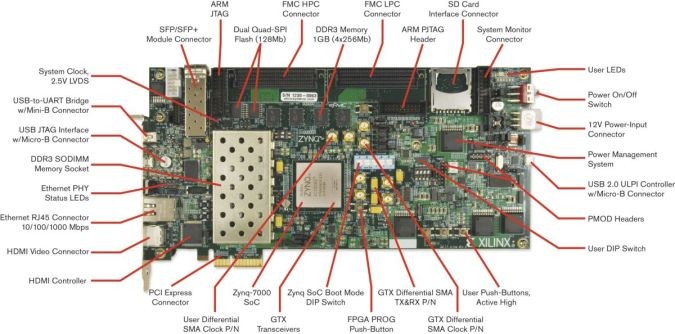

Zynq®-7000 SoC ZC706 评估套件包含硬件,设计工具, IP 核 以及预验证参考设计的所有基本元件,包括一个目标设计,可实现完整的嵌入式处理平台和基于收发器的设计-包含 PCIe 。 随套件提供预验证参考设计和行业标准 FPGA 夹层连接器(FMC),能够利用子卡实现升级和定制。请查看 PetaLinux 软件开发套件页面,了解 Xilinx 处理系统的信息。

主要性能和优势

- 使用 Zynq-7000 SoC 对嵌入式应用进行快速原型设计以实现优化

- 硬件、设计工具、IP、以及预验证参考设计

- 演示嵌入式设计,面向视频通道

- 高级存储接口

- 1GB DDR3 组件存储

- 1GB DDR3 SODIM 存储器

- 实现 PCIe Gen2x4、SFP+ 和 SMA 对、USB OTG、 UART、 IIC 的串行连接

- 支持包含 Dual ARM Cortex-A9 核处理器的嵌入式处理

- 使用 10-100-1000 Mbps Ethernet (RGMII) 开发网络应用

- 使用 HDMI 输出实现视频显示应用

- 扩展 I/O,包含 FPGA Mezzanine Card (FMC) 接口

特色 Xilinx 器件

包含符合 ROHS 的 ZC706,包括 XC7Z045 FFG900 – 2 SoC

| 逻辑单元 | 350 |

|---|---|

| Block RAM (Mb) | 19.1 |

| DSP Slice | 900 |

| 最大 I/O 引脚 | 362 |

| 最大收发器数量 | 16 |

电路板特性

包含 ZC706 评估板

通信与网络

- PCIe Gen2x4

- SFP+ 和 SMA 对

- RGMII 千兆以太网 (PS)

- USB OTG 1 (PS) - 主机 USB

- IIC 总线头/HUB (PS)

- 支持 CAN 唤醒的 1 CAN (PS)

- USB UART (PS)

扩展连接器

- 第一个 FMC LPC 扩展端口 (1个 GT 接口和 34 对 LVDS 的 LA 总线)

- 第二个 FMC HPC 扩展端口 (8个 GT 接口和 34 对 LVDS 的 LA 总线 – 无 HA 或 HB 总线)

- 双重 Pmod(与 LED 共享 8 个 I/O)

- 单个 Pmod (4 I/O)

- IIC 支持 8个I/O 访问

控制 & I/O

- 2个用户按钮开关/DIP 开关、2个用户 LED

- IIC 支持 GPIO 访问

- SDIO (SD 卡槽)

- 3个用户按钮开关2个用户按钮开关

- IIC 支持 8个I/O 访问

- IIC 支持 WTClock 访问

时钟技术

- 33MHz PS 系统时钟

- 200MHz PL 振荡器(单端与差分)

- 用于外部时钟(差分)的 SMA 接口

- 带有2个 SMA 连接器的 GTX 参考时钟端口

- OBSAI/CPRI - SFP+ 接收时钟

- EXT 配置时钟

配置

- 板上配置电路

- 2X16MB 四重 SPI 闪存

- SDIO 卡接口(启动)

- PC4 和 20 引脚 JTAG 端口

存储器

- DDR3 组件内存 1GB (PS)

- DDR3 SODIM 存储1GB (PL)

- 2X16MB 四重 SPI 闪存 (config)

- IIC - 1 KB EEPROM

模拟

- AMS 接口 (模拟) 系统监控器,亦可用于外部传感器

功耗

- 12 V 墙上适配器

- 具有电流测量功能的电源

特色 Xilinx 器件

包含符合 ROHS 的 ZC706,包括 XC7Z045 FFG900 – 2 SoC

| 逻辑单元 | 350 |

|---|---|

| Block RAM (Mb) | 19.1 |

| DSP Slice | 900 |

| 最大 I/O 引脚 | 362 |

| 最大收发器数量 | 16 |

内含物件

ZC706 评估板

包含 XC7Z045 FFG900 -2 SoC

整套 Vivado® Design Suite: Design Edition

Zynq-7000 XC7Z045 SoC 节点锁定 & 器件锁定,包含 1 年更新及技术支持

以太网电缆

ATX PCIe Minifit Jr 电源适配器

USB 适配器

USB Mini 电缆

HDMI 电缆

USB Micro 电缆

电源电线和适配器

设计工具与下载

| Name | Description | License Type | Files |

|---|---|---|---|

| Vivado Design Suite | The Xilinx Vivado® Design Suite is a revolutionary IP and System Centric design environment built from the ground up to accelerate the design for FPGAs and SoCs. | Node locked and device-locked to the XCZU7EV MPSoC FPGA, with one year of updates | Download Vivado Design Suite |

| Vitis Unified Software Platform | Full suite of tools for embedded software development, hardware acceleration, and debug targeting Xilinx platforms. | Free | Download Vitis Embedded Platforms |

| PetaLinux Tools | Configure, Build, and Deploy Linux operating system to Xilinx platforms. | Free | Download Petalinux Tools |

其他工具、IP 和资源

Default

Default

标题

日期