Xilinx Platform Studio(XPS)

Xilinx Platform Studio (XPS) 是 ISE 嵌入式版本 Design Suite 的关键组件,可帮助硬件设计人员方便地构建、连接和配置嵌入式处理器系统,能充分满足从简单状态机到成熟的 32 位 RISC 微处理器系统的需求。

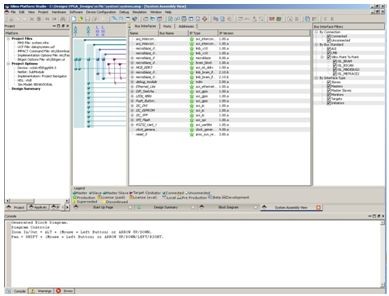

XPS 采用图形设计视图和通过设计校正的高级向导能帮助开发人员一步步完成创建定制系统所需的步骤,且用时不过几分钟而已。

XPS 的真正潜力体现在它能配置和集成 /Xilinx 嵌入式 IP 核目录中的即插即用IP核以及定制和第三方 Verilog 及 VHDL 设计。

固件和软件开发者受益于 XPS 与 Xilinx SDK 的集成,从而能自动生成关键的系统软件,如引导载入程序、裸金属 BSP 和 Linux BSP 等。上述功能可确保 OS 移植和应用开发能及时启动,而不会因为固件开发而延误。

Zynq®-7000 SoC 通过集成 ARM Cortex A9 双核微处理器和具有以太网、I2C、SDIO、USB 和 CAN 等功能的硬外设集,从而可提供 SoC 的尖端功能,并配套提供 Xilinx 可编程逻辑,能将定制软外设、逻辑、器件和加速器进行实例化。 XPS 通过易于使用的图形向导可加速 Zynq 器件设计的方方面面,包括用于硬外设的时钟域设置、中断、DMA 和外部连接以及用于可编程逻辑中软外设的接口连接等。 这意味着设计人员能立即启动定制设计,而无需担心接口或连接的定义不兼容。

- AXI 接口

- 通用型 32 位 AXI 主/从端口

- 高速 32/64 位 AXI 从端口

- 64 位 AXI 加速器连接端口

- 通用 DMA 控制器

- 系统、外设、跟踪和调试时钟

- 加固型 Zynq-EPP 外设接口

- Quad SPI/SRAM/NOR/NAND Flash

- 千兆位级以太网

- USB 2.0

- 安全数字

- UART

- I2C

- SPI

- CAN

- GPIO

- 中断

- 外设连接至多路复用 I/O

Xilinx Microblaze™ 具有出色的可扩展性和可定制潜力,能够满足 8 位状态机到复杂 SoC 型 32 位 RISC 设计的要求,并且可支持各种项目的具体处理要求。工程师利用 XPS 集成预验证的处理器内部 IP(如流水线、时钟、计时器和中断控制器)和处理器外设 IP 核(如存储器控制器、USB、CAN 总线、I2C、以太网、FPU 等)可创建出成百上千种不同的 Microblaze 设计(通过 /Xilinx 嵌入式 IP catalog 提供)。这种现有的处理器配置功能结合集成第三方 RTL 和定制 IP 块的功能,能够帮助工程师推出真正独特的定制设计,从而充分满足具体的需求。

XPS 在定制处理器设计中支持 Xilinx 嵌入式 IP catalog 下 IP 核的拖放集成。这种 IP 核包括外设、器件和加速器,如 AXI 桥接器、GPIO、PLBV4.6 桥接器、BRAM 和外部存储器控制器、串行外设和 QuadSPI 接口、模数转换器、图形、时钟和计时器、UART、I2C、中断控制器乃至更多。

虽然 Xilinx 目录中的外设可创建多种系统,通常我们仍需要为新功能创建并导入定制外设。Xilinx 的创建和导入外设向导能让硬件设计人员用 Verilog 或 VHDL(也可二者同时使用,针对混合语言设计)创建 AXI(第四版)外设并导入到 XPS 项目中,连接于任何 AXI4-Lite、AXI4(启用 Burst)和 AXI4-Stream 接口。该向导还能让您集成 PLB(4.6 版本)或 FSL 外设 PLB 设计。导入 XPS 时,定制外设的管理与 Xilinx 嵌入式 IP 核目录提供的现有模块一样。

XPS 可简化每个 IO 引脚的连接或内部可编程逻辑端点到适当端点的连接。 XPS 能方便地管理连接,通过物理接口连接片外,也可连接到可编程逻辑中的其它器件,确保适当路由、信号和电压轨的准确性。对 Zynq-7000 SoC 器件系列而言,XPS 还能够管理内置 IO 多路复用器的配置,可路由处理系统器件到适当的输出引脚。

采用 Xilinx FPGA 或 Zynq-7000 SoC 等可编程逻辑创建的定制设计需要定制固件全程管理定制硬件,从一级启动到器件实例化(比特流)到初始化直到器件具体接口(通过软件堆栈)。 由于固件开发和定制硬件设计之间的严格相关性,这种固件的创建可能非常具有挑战性。XPS 同 Xilinx SDK 共享硬件、项目和针对具体设计的信息,而 SDK 则能自动配置、构建和部署针对具体设计的关键固件,包括:

- 第一级引导载入程序

- 安全软件(引导载入程序、固件)

- 比特流管理

对来自 Xilinx 嵌入式 IP 核目录的器件,SDK 还能自动生成金属裸面驱动程序和 BSP,可加入无 OS 的代码或 RTOS,也可生成 Linux 驱动程序和 BSP。这样,XPS 就能让设计人员基本不用再担心固件和低级 BSP 开发问题了,避免为启动、OS 和应用开发操心。

XPS 的优势

| Xilinx - 硬件感知 |

|

| Xilinx 嵌入式 IP Catalog 集成 |

|

| 图形配置向导 |

|

| 确保正确的连接功能 |

|

| 集成/连接至 Xilinx 工具流程 |

|