AR# 35169

|MIG Virtex-6 DDR2/DDR3 - Determining which calibration stage failed

描述

When phy_init_done does not assert, signifying a calibration failure, it is important to first identify which stage of calibration failed.

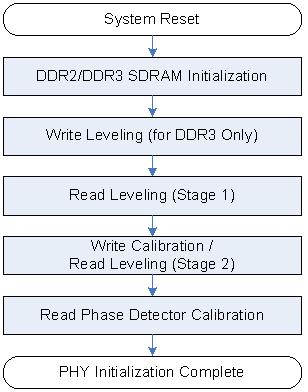

The MIG Virtex-6 DDR2/DDR3 FPGA design goes through the following calibration stages:

This series of calibration debug Answer Records focus on debugging Write Leveling, Read Leveling Stage 1, and Write Calibration / Read Leveling Stage 2.

NOTE: This Answer Record is contained in a series of MIG hardware debug Answer Records and assumes you are running the MIG Example Design with the Debug Port Enabled. It is best to start at the beginning of this recommended hardware debug flow; see (Xilinx Answer 34588)

NOTE: This Answer Record is part of the Xilinx MIG Solution Center (Xilinx Answer 34243) The Xilinx MIG Solution Center is available to address all questions related to MIG. Whether you are starting a new design with MIG or troubleshooting a problem, use the MIG Solution Center to guide you to the right information.

解决方案

NOTE: These steps assume the Example Design with the Debug Port is running in your hardware.

If this design is not loaded in your hardware, please go to (Xilinx Answer 34588)

Write Leveling Failures (DDR3 Only)Signals of Interest:

- dgb_wrlvl_start = Memory Initialization Completed Successfully and Write Leveling Begins.

- dbg_wrlvl_done = Write Leveling Completes Successfully.

- dbg_wrlvl_err = Write Leveling Fails.

Read Leveling Stages 1 and 2

NOTE: The calibration algorithm is designed so that Read Leveling Stage 1 never triggers an error.

An error during Read Leveling would always be seen during Read Leveling Stage 2.

If a failure is detected during Read Leveling Stage 2, it is crucial to start the debug during Read Leveling Stage 1 and then move to the Read Leveling Stage 2 section.

For full details on why Stage 1 does not trigger an error, see (Xilinx Answer 35074)

Signals of Interest:

dbg_rdlvl_done[1:0]

- 2'b00 = Stage 1 and Stage 2 did not finish.

- 2'b01 = Stage 1is complete, stage 2 has not finished.

- 2'b11 = Read Leveling completed successfully.

dbg_rdlvl_err = Indicates when an error occurs during Read Leveling Stage 2 (see above note on Stage 1 failures).

For information on Read Leveling Stage 1 Debug, see (Xilinx Answer 35183)

For information on Read Leveling Stage 2 Debug, see (Xilinx Answer 35193)

For generation information on usage of the Debug Port, see (Xilinx Answer 35206)

链接问答记录

相关答复记录

| Answer Number | 问答标题 | 问题版本 | 已解决问题的版本 |

|---|---|---|---|

| 35206 | MIG Virtex-6 DDR2/DDR3 - Usage of Debug Port | N/A | N/A |

| 35193 | MIG Virtex-6 DDR2/DDR3 - Debugging Read Leveling Stage 2 | N/A | N/A |

| 35183 | MIG Virtex-6 DDR2/DDR3 - Debugging Read Leveling Stage 1 | N/A | N/A |

| 35177 | MIG Virtex-6 DDR3 - Debugging Write Leveling Failures | N/A | N/A |

| 34743 | MIG Virtex-6 DDR2/DDR3 - Debugging Calibration Failures | N/A | N/A |

| 34588 | MIG Virtex-6 DDR2/DDR3 - Board Debug including general debug, calibration debug, and data error debug | N/A | N/A |