AR# 38408

|Spartan-6 IODELAY2 设计咨询 - 后期和早期边缘延迟 以及单个数据位损坏

描述

Spartan-6 FPGA 器件中的 IODELAY2 模块会遇到 后期数据沿延迟、早期数据沿延迟 和单一数据位损坏。Spartan-6 FPGA 生产勘误表 (EN148) 针对所有生产状态 Spartan-6 FPGA 器件中存在的这一问题已进行了更新:

//m.alegre-web.com/support/documentation/errata/en148.pdf

此答复记录说明了旧掩膜版本器件的行为。

有关新掩膜版本器件的详细信息,请参阅(Xilinx 答复 41083)。 有关如何区分新/旧掩膜版本的详细信息,请参阅 XCN11012。

XA 汽车、XQ、Q 级和 XC 低功耗 -1L 器件仅随新掩膜版本推出。

注:MCB 将不受此问题影响。

解决方案

IDELAY 和 ODELAY 模式中的后期数据沿延迟当所有 IDELAY_TYPE 设置中的 IDELAY_VALUE 或 ODELAY_VALUE 为 4 或更高值时或这些值用作输出延迟时,IODELAY2 模块可在上升沿或下降沿转换中将延迟增加高达 350 ps。

可以在所有数据速率中出现此行为,并且该行为应包含在系统时序裕量分析中。

后期数据沿延迟解决方法:

没有有效的方法来解决后期数据沿延迟问题,您必须在系统时序裕量分析中考虑到这一问题。有关考虑 潜在延迟变化 的时序约束说明,请参见(Xilinx 答复 39046)。

ODELAY 模式中的早期数据沿延迟

ODELAY 模式中的 IODELAY2 模块可在上升沿或下降沿转换过程中,使数据沿的早期延迟达 350 ps。早期数据沿要早于预期或通常的数据沿。在数据速率超过 533 Mb/s 以及在所有 ODELAY_VALUE 设置中都会出现此行为,并且应该将其包含在系统时序裕量分析中。

早期数据沿延迟解决方法

没有有效的方法来解决增加的数据沿延迟问题,您必须在系统时序裕量分析中考虑到这一问题。有关考虑 潜在延迟变化 的时序约束说明,请参见(Xilinx 答复 39046)。

IDELAY 和 ODELAY 模式中的单一数据位损坏

IODELAY2 模块会损坏所有 IDELAY_TYPE 设置的单一数据位或用作输出延迟的单一数据位。

单一数据位损坏解决方法

具体的解决方法将建立在 IDELAY_TYPE 设置的基础上。

下列指南建议您基于使用 IODELAY2 所在的模式来限制 IODELAY2 的使用。请注意,IDELAY_TYPE 是定义操作模式的属性,它与 IDELAY_MODE 或 SERDES_MODE 属性无关。还需注意的是,所有性能限制均基于实际的数据速率,而不是时钟频率。这些值与是否使用 SDR 或 DDR 或 ISERDES2 DATA_RATE 属性无关。

- IDELAY_TYPE=DEFAULT - 数据速率必须小于 250 Mb/s 才能避免数据损坏。此模式最常用于低速寄存输入,这样才能将影响视为最低。

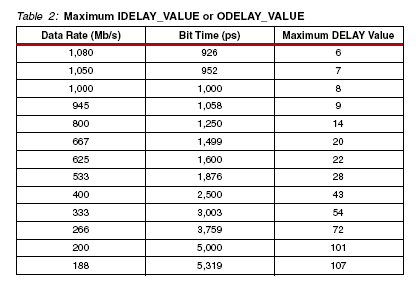

- IDELAY_TYPE=FIXED 或 VARIABLE_FROM_ZERO 或在 ODELAY 模式中使用- IDELAY_VALUE 或 ODELAY_VALUE 必须小于表 2 中的值,才能避免在指示的数据速率中出现数据损坏。

- IDELAY_TYPE=VARIABLE_FROM_HALF_MAX - 数据速率必须小于 400 Mb/s,IODELAY2 IOCLK 频率必须等于数据速率,并且积极增量必须小于 5 才能避免数据损坏。

- IDELAY_TYPE=DIFF_PHASE_DETECTOR - 数据速率必须小于 400 Mb/s,当数据速率小于或等于 400 Mb/s 时,数据时钟歪斜(包括数据包跟踪差异)必须小于 0.15 个单位间隔 (UI) 才能避免数据损坏。在本例中,数据时钟歪斜表示时钟沿不得在进入数据脉冲或数据脉冲之后出现的单位间隔超过 0.15 UI。 0.15 UI 准则与后期时钟强制节拍值增量的事实有关,因此太多的时钟歪斜会造成节拍超过所支持的范围。

受影响的器件

- 这些问题会影响所有 Spartan-6 旧掩膜版本器件。 有关如何区分新/旧掩膜版本的详细信息,请参阅 XCN11012。

- 有关此问题会对 Spartan-6 新掩膜版本器件产生哪些影响,请参阅 (Xilinx 答复 41083)。

- 有关此问题会对 -1L 器件产生哪些影响,请参阅(Xilinx 答复 41356)。

故障特性

- 额外的沿延迟、数据损坏或在一个引脚上可能同时出现这两种问题。

- 避免数据损坏的解决方法不会禁止额外的沿延迟。

- 故障是间歇性的

- 固定模式中的最大节拍限制点位于超过 400 Mb/s 的所有数据速率的中点之前的位置。这会使可变模式(VARIABLE_FROM_HALF_MAX)中的节拍限制等于或小于 400 Mb/s。

风险

整体故障率很低,它与数据速率以及使用的 IODELAY2 元素数量有关。

存储器控制模块

请注意, 存储器控制模块 (MCB) 接口不受 IODELAY2 问题的影响。

软件/用户指南

目前解决此问题的软件或用户指南没有更新。

其他指南

以下提供的其他指南可帮助设计上述解决方法。在将 IDELAY_TYPE 用作 VARIABLE_FROM_ZERO 或 VARIABLE_FROM_HALF_MAX 时,请务必 监控当前的节拍值,以便它与指定的值不相冲突。为此,请设计一个计数器线路,在每次增加您的节拍延时值时增加“1”,在每次减少您的节拍延时值时减去“1”。可以监控该值以确保节拍值不超过指定的值,从而避免出现单一数据位损坏。

- 请不要逐比特去歪斜,而应使用时钟去歪斜以最大限度地减少易受影响的引脚数量。

- 请联系您的现场应用工程师或提交服务请求以获取 Xilinx 技术支持://m.alegre-web.com

链接问答记录

主要问答记录

| Answer Number | 问答标题 | 问题版本 | 已解决问题的版本 |

|---|---|---|---|

| 34856 | Design Advisory Master Answer Record for Spartan-6 FPGA | N/A | N/A |

相关答复记录

| Answer Number | 问答标题 | 问题版本 | 已解决问题的版本 |

|---|---|---|---|

| 46791 | Spartan-6 FPGA Design Assistant - Troubleshoot Common Fabric Problems | N/A | N/A |

| 41356 | Design Advisory for Lower Power Spartan-6 -1L Speed Grade - IODELAY2 Support Restricted to Tap 0 | N/A | N/A |

| 39046 | Spartan-6 IODELAY2 - Late Data Edge and Early Data Edge Timing Analysis | N/A | N/A |

| 34856 | Design Advisory Master Answer Record for Spartan-6 FPGA | N/A | N/A |

| 41083 | Design Advisory for Spartan-6 IODELAY2 - IODELAY2 Data Rate and Corresponding Bit Error Rates for New Mask Revision Silicon | N/A | N/A |

| AR# 38408 | |

|---|---|

| 日期 | 03/02/2017 |

| 状态 | Active |

| Type | 设计咨询 |

| 器件 | |