AR# 40191

|7系列器件 - 1.8V LVDS和2.5V LVDS 信号之间的LVDS兼容性

描述

对于带LVDS输出的高性能(HP)I/O组,7系列FPGA的VCCO电平应为1.8V。

LVDS兼容的驱动器或接收器存在兼容性问题吗?

解决方案

当连接LVDS-可兼容的驱动器与接收器时,7系列器件的LVDS和LVDS_25的输入和输出不会存在兼容性问题。

对TIA/EIA-644 LVDS兼容器件, 该标准给出了输入输出的差分及共模电压的上下限。

7系列器件的数据手册列举了Xilinx 7系列器件的LVDS(HP组)和LVDS_25(HR组)输入和输出的电气特性。

手册中的列举的这些输出或输入电气特性,完全符合TIA/EIA-644可兼容接收机或TIA/EIA-644 可兼容驱动器的要求。

若因为某种原因,某器件不兼容标准LVDS(TIA/EIA-644),这时设计者或可改变或修改开发板的终端设计以满足驱动器与接收器的特性要求。

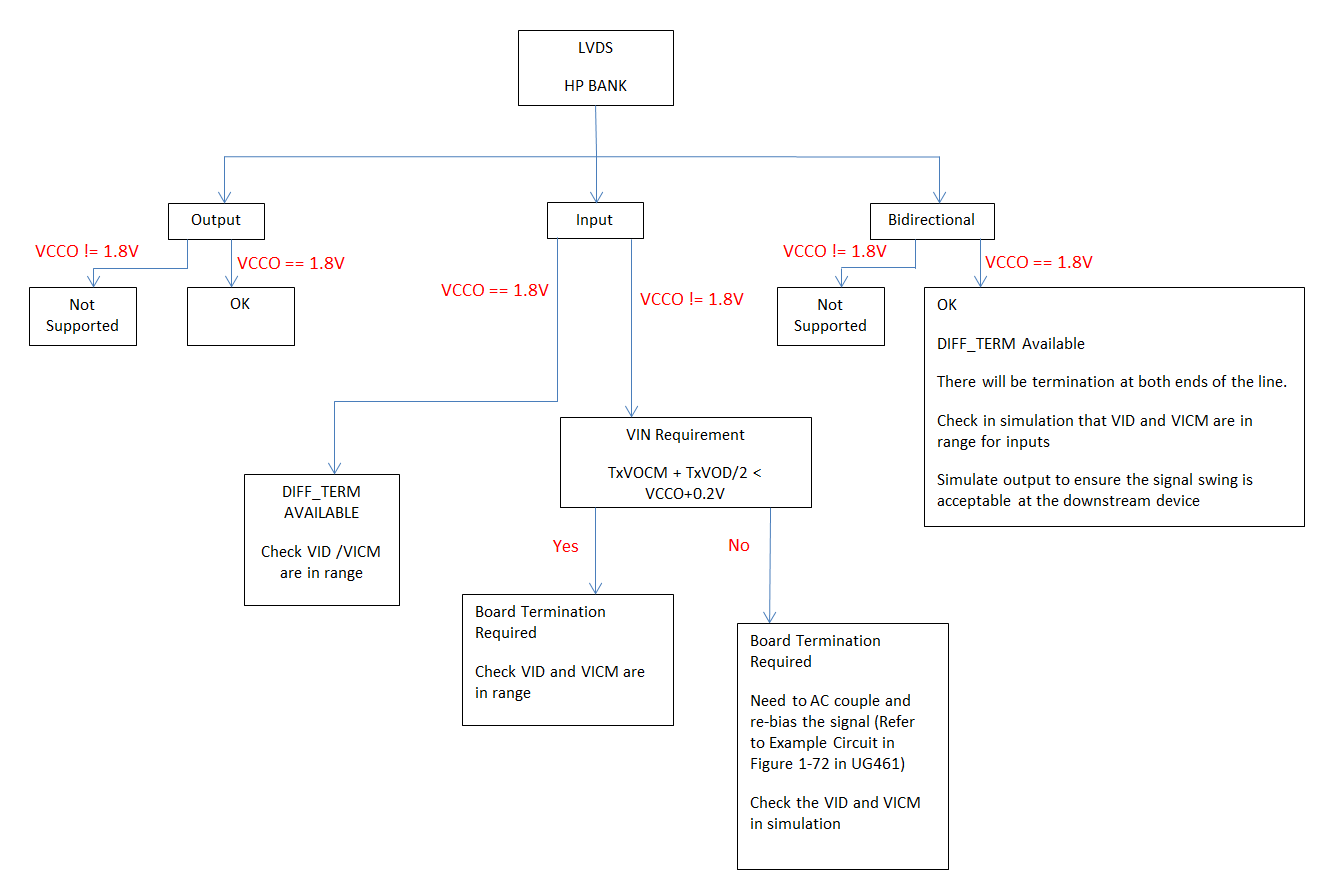

当在高性能库中使用 LVDS 连接时,您可以参考清单以确保发信号正常运作。

本答复记录是否对您有帮助?

链接问答记录

主要问答记录

| Answer Number | 问答标题 | 问题版本 | 已解决问题的版本 |

|---|---|---|---|

| 47900 | SelectIO Design Assistant: Interfacing to Xilinx devices | N/A | N/A |

相关答复记录

| Answer Number | 问答标题 | 问题版本 | 已解决问题的版本 |

|---|---|---|---|

| 41408 | 7 Series - How to place LVDS in a High Performance bank | N/A | N/A |