AR# 43428

|Spartan-6 - Can I use Sub-LVDS as input to a Spartan-6 FPGA I/O?

描述

Is it possible to drive a Spartan-6 FPGA I/O with a Sub-LVDS input?解决方案

It is possible, however, the electrical characteristics of the Sub-LVDS input need to be checked to ensure that it meets the Spartan-6 FPGAinput requirements.

Take the following Sub-LVDS specifications:

| Parameter | Min | Typical | Max | Unit |

| Fixed common mode voltage VCMF | 0.8 | 0.9 | 1.0 | V |

| Differential voltage swing VOD | 100 | 150 | 200 | mV |

| Drive current range | 0.833 | 1.5 | 2 | mA |

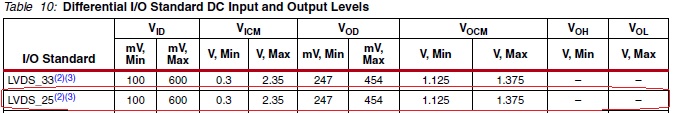

In the case above the Standard LVDS input buffer can be used:

For the input swing VID Min/ Max 100mV / 600mV the Sub-LVDS is 100 / 200mV; so, this is within spec.

The LVDS common mode it is 0.3mV -> 2.35V and the Sub-LVDS is 0.8mV -> 1V; which is also within spec.

The normal LVDS termination can be used. However, an IBIS simulation should be done in all cases to ensure the signal integrity is correct.

本答复记录是否对您有帮助?

链接问答记录

主要问答记录

| Answer Number | 问答标题 | 问题版本 | 已解决问题的版本 |

|---|---|---|---|

| 47900 | SelectIO Design Assistant: Interfacing to Xilinx devices | N/A | N/A |

| AR# 43428 | |

|---|---|

| 日期 | 02/18/2013 |

| 状态 | Active |

| Type | 综合文章 |

| 器件 | |

People Also Viewed