AR# 53066

|14.4 AXI Ethernet IP - SDK fails during BSP build with system containing AXI Ethernet IP on Zynq

描述

In simple designs using the AXI Ethernet IP connected to the Zynq SoC, when compiling the BSP in SDK, the error below is shown on the console:

![]() ERROR:EDK - axiethernet () - Peripheral ps7_scugic_0 has 5 interrupt ports.

ERROR:EDK - axiethernet () - Peripheral ps7_scugic_0 has 5 interrupt ports.

Should have exactly one.

ERROR:EDK:3416 - Error(s) while running TCL procedure generate().

make: *** [ps7_cortexa9_0/lib/libxil.a] Error 2

make: Target `all' not remade because of errors.

How can I fix this?

解决方案

This is a known issue in the tools.

Attached to this answer record is an example XPS project targeting the ZC702 board with an AXI Ethernet IP in the Programmable Logic.

There is also, an updated AXI Ethernet driver and LwIP Library.

To use this project, download the attached ZIP, open the XPS project, and export to SDK.

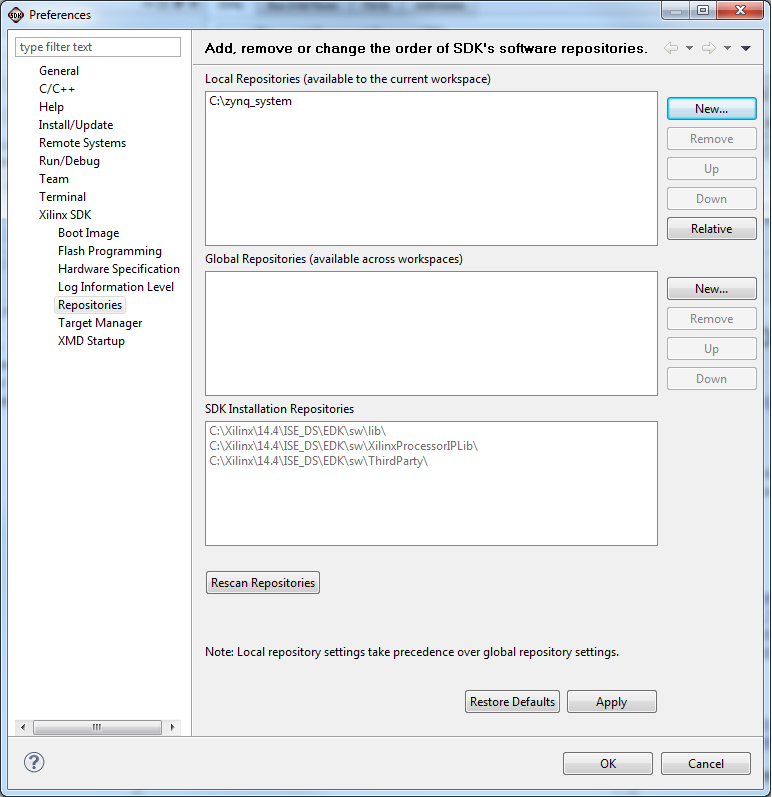

In SDK select Xilinx Tools -> Repositories.

Select New, and point to your project directory, then select Rescan Repositories:

This will allow for the updated AXI Ethernet and LwIP to be used when creating the BSP.

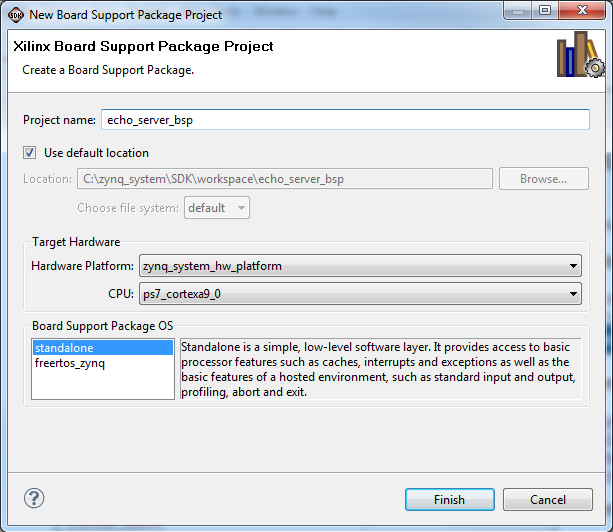

To create an Echo Server Application, select File -> New -> Board Support Package:

Select Finish to continue.

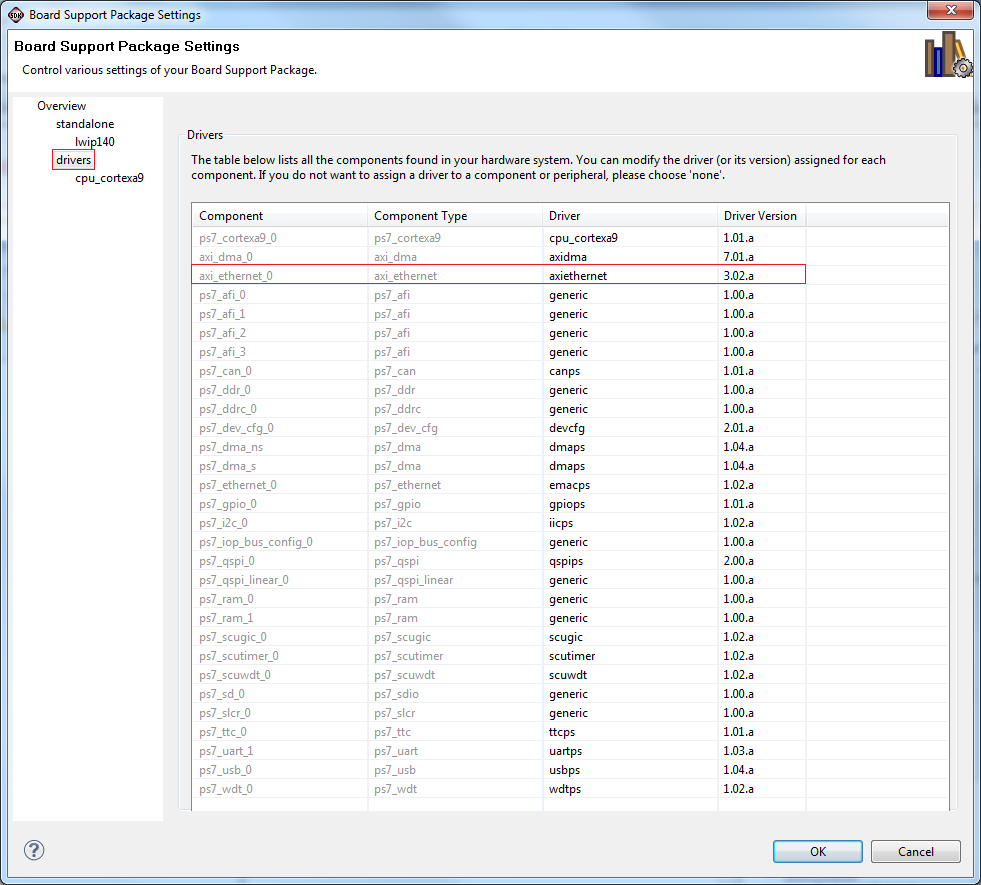

In the Board Support Package Settings, make sure that the AXI Ethernet driver version is set to 3.02.a:

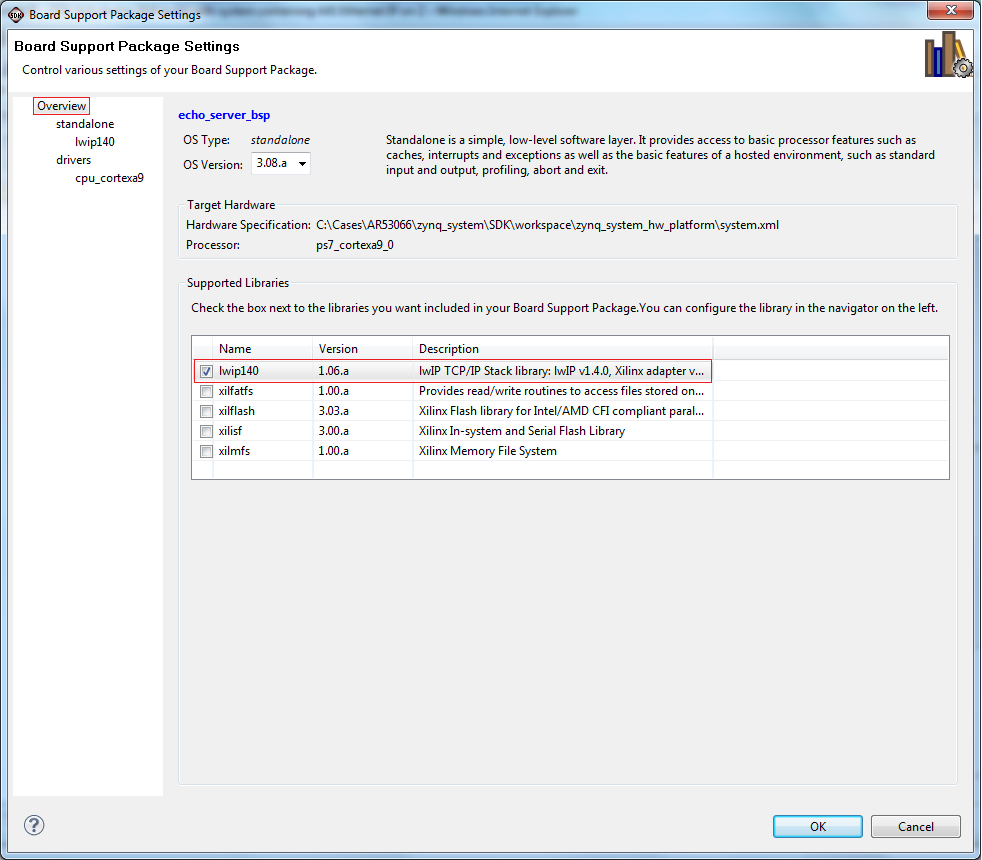

In the Overview Section, select the LwIP140 check box and set this to 1.06.a:

Select OK to continue.

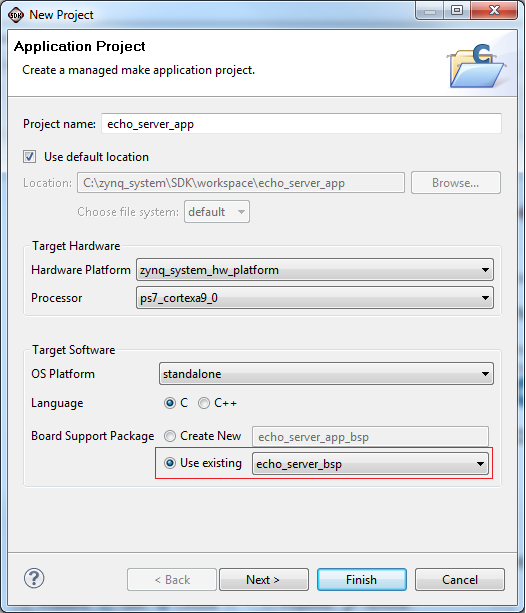

Next, create the LwIP Echo Server Application. To do this go to File -> New -> Application Project:

Select Next, then select the LwIP Echo Server:

Select Finish to Continue.

Note: The AXI Ethernet and the LwIP will not be fully supported on Zynq SoC until the 14.5 release.

附件

| 文件名 | 文件大小 | File Type |

|---|---|---|

| AR53066.zip | 12 MB | ZIP |