AR# 65228

|How to share a COMMON block using GTH transceivers

描述

This article documents the process used to share a COMMON block in UltraScale GTH transceivers.

It uses an example case of two different 10-lane protocols.

The principle applies to GTY transceivers as well.

解决方案

Transceiver Common Block sharing

The UltraScale GTH/GTY transceiver COMMON block has several PLLs which allow for multiple protocols to operate in the same group while using unrelated reference clocks and data rates.

The process to put together a design with a shared COMMON using the GT Wizard and the associated example designs is not fully automated and is considered an advanced use mode.

Here, a flow is presented demonstrating a case with two groups of 10 GTs, each using unrelated reference clocks.

These 20 GTHs are spread across 5 GTH COMMON blocks. Figure 1 shows the setup.

Please ensure that the reference clock sharing does not go across the boundary of SLRs.

If GTYs are used, the reference clock does not support a line rate greater than 16.3Gbps.

Overview

This example uses the Example Design setting for all possible options for several reasons.

First, to maintain continuity of GT configuration across all 10 lanes and to avoid the possibility of a mismatch on some of the lanes.

Second, the process was required to be able to be clearly documented and explained.

Lastly, the fundamental components can be re-used by others.

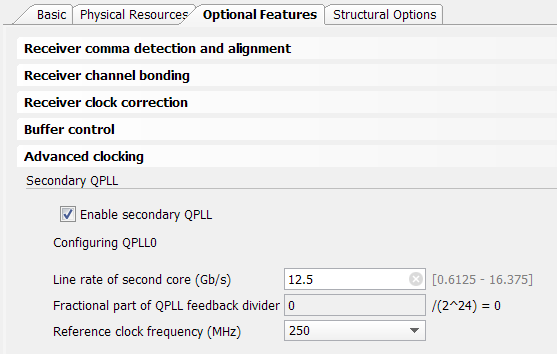

At a high level, the process consisted of constructing 2 10 lane interfaces using the GT wizard, being sure to include the COMMON block in the Example Design that the and secondary PLL functionality was enabled.

These example designs were then integrated into a top-level design and a shared common wrapper file which included instantiations for each of the COMMON blocks individually.

The necessary signals were then connected from the COMMON blocks to the top level, GT CHANNELs, and helper blocks.

The IP customization and design construction processes are explained in more detail in the following sections.

IP Customization

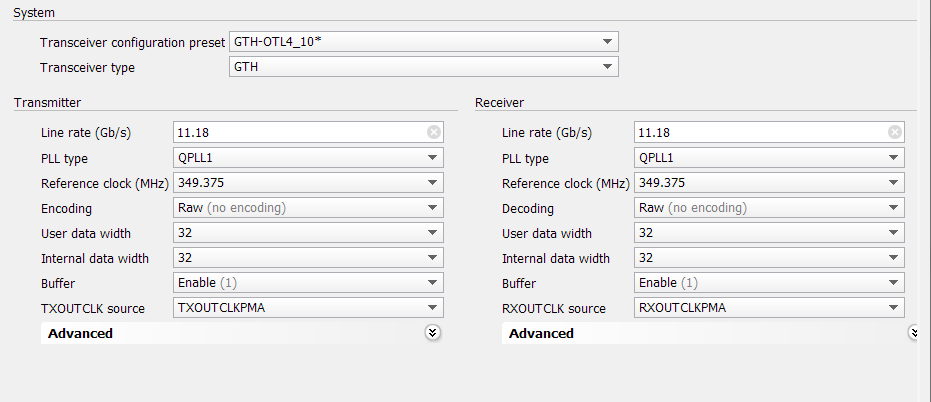

First is the OTL4.10 core, which includes the secondary PLL option.

Customize the OTL4.10 core

Enter the line rate and refclk frequency for the second set of GTs.

Customize the 10x12.5G core

a. Basic tab

- Line rate 12.5Gb/s

- QPLL0

- Refclk 250MHz

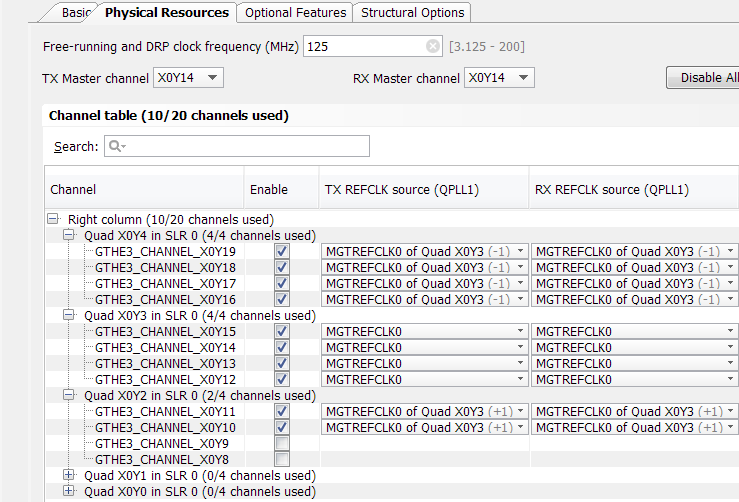

b. Physical Resources tab

- Select GTs, associated refclks, Master channel, and DRP clk freq.

c. Optional features tab

- Leave set to defaults.

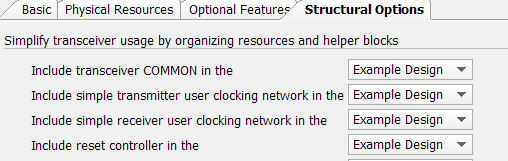

d. Structural options tab

- Ensure COMMON is in the example design.

Design construction

The version I created is attached and described in the figure below.

COMMON 1 corresponds to the OTL4.10 version that has the Enable Secondary PLL option selected.

Either COMMON 1 or COMMON 2 can be used for X0Y0 and X0Y1.

Note: Ensure X0Y2 is COMMON 1 - with "Enable Secondary PLL" selected.

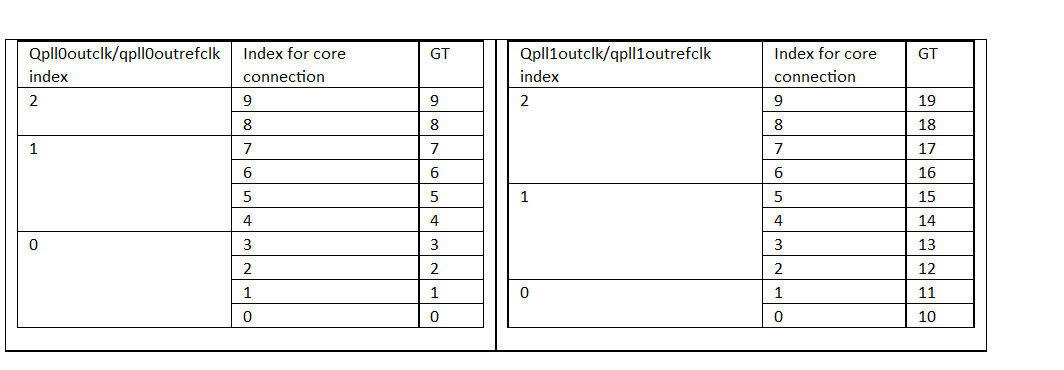

11. For each set of 10 GTs, inside the example_wrapper_inst level of hierarchy, wire out the corresponding PLL signals and connect to the GTH_COMMONS as described below.

The GT number corresponds to the index in the bus connected to the core:

Validate

The design successfully routed and the schematic was correct.

附件

| 文件名 | 文件大小 | File Type |

|---|---|---|

| gth_commons.v | 18 KB | V |

| AR# 65228 | |

|---|---|

| 日期 | 08/28/2015 |

| 状态 | Active |

| Type | 综合文章 |

| 器件 | |

| Tools | |

| IP | |