AR# 71466

|DMA Subsystem for PCI Express (Vivado 2018.2) - ERROR: [Place 30-69] Instance xdma_app_i/led_2_obuf (OBUF drives I/O terminal xdma_app_i/leds[2]) is unplaced after IO placer

描述

An IP example design using the "Tandem with field updates" option generates the following errors and critical warnings when the executing design_field_updates.tcl script.

CRITICAL WARNING: [filemgmt 56-226] HADGDesignGraphMgr::releaseGraph: Graph could not be found.

WARNING: [Vivado 12-584] No ports matched 'led_0'. [/xdma_0_ex/imports/xilinx_pcie_xdma_ref_board.xdc:97]

CRITICAL WARNING: [Common 17-55] 'set_property' expects at least one object. [/xdma_0_ex/imports/xilinx_pcie_xdma_ref_board.xdc:97]

Resolution: If [get_<value>] was used to populate the object, check to make sure this command returns at least one valid object.

WARNING: [Vivado 12-584] No ports matched 'led_1'. [/xdma_0_ex/imports/xilinx_pcie_xdma_ref_board.xdc:99]

CRITICAL WARNING: [Vivado 12-4739] set_false_path:No valid object(s) found for '-to [get_ports -filter NAME=~led_*]'. [/xdma_0_ex/imports/xilinx_pcie_xdma_ref_board.xdc:109]

CRITICAL WARNING: [Common 17-55] 'set_property' expects at least one object. [/xdma_0_ex/imports/xilinx_pcie_xdma_ref_board.xdc:97]

Resolution: If [get_<value>] was used to populate the object, check to make sure this command returns at least one valid object.

WARNING: [Vivado 12-584] No ports matched 'led_1'. [/xdma_0_ex/imports/xilinx_pcie_xdma_ref_board.xdc:99]

CRITICAL WARNING: [Vivado 12-4739] set_false_path:No valid object(s) found for '-to [get_ports -filter NAME=~led_*]'. [/xdma_0_ex/imports/xilinx_pcie_xdma_ref_board.xdc:109]

........................................

ERROR: [Place 30-69] Instance xdma_app_i/led_2_obuf (OBUF drives I/O terminal xdma_app_i/leds[2]) is unplaced after IO placer

ERROR: [Place 30-68] Instance xdma_app_i/led_2_obuf (OBUF) is not placed

ERROR: [Place 30-99] Placer failed with error: 'IO Clock Placer failed'

Please review all ERROR, CRITICAL WARNING, and WARNING messages during placement to understand the cause for failure.

17 Infos, 1 Warnings, 0 Critical Warnings and 4 Errors encountered.

place_design failed

ERROR: [Common 17-69] Command failed: Placer could not place all instances

This article is part of the PCI Express Solution Centre

| (Xilinx Answer 34536) | Xilinx Solution Center for PCI Express |

解决方案

The xdma_app.v module has an "leds" output port.

This output is expected to be connected to led_0, led_1, led_2 and led_3 ports in the example design top file.

Follow the steps below to resolve this issue.

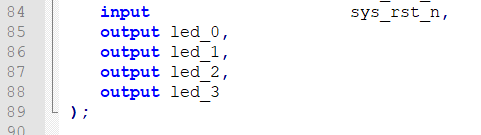

1) Add the output ports led_0, led_1, led_2, led_3.

2) Connect the leds output from the xdma_app module instance to the output ports.

3) Add the following Tcl commands in the static_synth.tcl file before the synth_design command.

# Disable DRC relating to unconnected IO on the PR region. This is intentional as

# the provided design is an example design rather than completed design.

set_msg_config -id {Constraints 18-952} -new_severity {Warning}

# Disable DRC relating to unconnected IO at the PR region boundary relating to the

# PR region debug bridge IP.

set_msg_config -id {Synth 8-4442} -new_severity {Warning}

Revision History:

- 11/14/2018 - Initial Release

本答复记录是否对您有帮助?

| AR# 71466 | |

|---|---|

| 日期 | 11/14/2018 |

| 状态 | Active |

| Type | 综合文章 |

| 器件 | |

| Tools | |

| IP | |

People Also Viewed