隔离设计流程

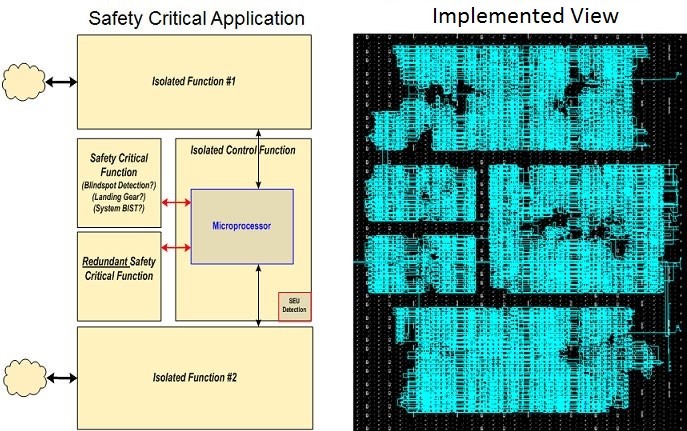

安全关键应用中的故障容错

通过容错设计掌控系统失效模式需要确保故障传播可控的实现方法。Xilinx 隔离设计流程(IDF)通过多种技术提供了在 FPGA 模块层次的容错,并实现了单芯片容错,这些技术包括:

- 模块化冗余

- 看门狗报警

- 根据安全级别隔离

- 安全去除测试逻辑隔离

隔离设计流程率先用于政府密码系统,后也适用于航空电子设备、功能安全相关的电子产品、工业机器人、关键基础设施、金融系统和其他高安全、高可用性、高可靠性的系统。隔离设计流程是可靠性技术系列的一部分,通过适当组合可提供无与伦比的可靠性、性能和成本效率。

除了政府级别加密系统的悠久服务传统,IDF也是Xilinx IEC61508 (工业功能安全) 标准工具链的组成部分。此外,它可以帮助产品满足 ISO26262 规范要求(汽车性能安全)。

器件和软件支持

* 仅 7S50

IDF 方法

文档和参考设计

Virtex-5 FPGA

- Virtex-5 SCC

XAPP1134,“利用 Virtex-5 系列开发的安全设计”,帮助 FPGA 设计者 实现 Xilinx SCC 技术。 - 使用 ISE 11.4 / 11.5 Design Suite 的 SCC

XAPP1135,“使用 Virtex-5 系列 Pro/ ISO 流程进行单芯片加密实验”, 帮助 FPGA 设计者使用 ISE 11.4 / 11.5 Design Suite 实现 Xilinx SCC 技术。 - 使用 ISE 12.1 / 12.4 Design Suite 的 SCC

XAPP1105,“使用面向 ISE 12.1 的 Virtex-5 系列 Pro/ ISO 流程进行单芯片加密实验”,帮助 FPGA 设计者使用 ISE 12.1 / 12.4 Design Suite 实现 Xilinx SCC 技术。

Spartan-6 FPGA

- 面向 Spartan- 6 的隔离设计流程(IDF)

XAPP1145,“通过隔离设计流程用 Spartan-6 系列上开发安全设计”,有助于 FPGA 设计师实现安全设计。 - 使用 ISE 12.4 Design Suite 的隔离设计流程实验(Isolation Design Flow Lab)

XAPP1104,“用 ISE Design Suite 12.4 在 Spartan-6 系列实现自动防故障设计'',帮助 FPGA 设计者使用隔离设计流程实现安全设计。

7系列 FPGA

ISE Design Suite

- 面向 7 系列的隔离设计流程(IDF)规则/指南

XAPP1086,” 通过隔离设计流程用 Xilinx 7 系列 FPGA 开发安全可靠的单 FPGA 设计”,帮助 FPGA设计者实现安全设计。 - Kintex-7: 使用 ISE 14.4 Design Suite 的隔离设计流程 (IDF) 实验

XAPP1085, "使用 ISE Design Suite 14.4 进行 7 系列隔离设计流程(IDF)实验", 帮助 FPGA 设计者使用隔离设计流程实现安全设计。

Vivado Design Suite

- 面向 7 系列 (Vivado 工具) 的隔离设计流程(IDF)规则/指南

XAPP1222,” 面向 Xilinx 7 系列 FPGA 或 Zynq-7000 SoC (Vivado 工具) 的隔离设计流程”,帮助 FPGA 设计者实现安全设计。 - Zynq-7000: Vivado 隔离设计流程 (IDF) 实验

XAPP1256, ''Zynq-7000 SoC 隔离设计流程实验 (Vivado Design Suite 2015.2)'', 帮助 FPGA 设计者使用隔离设计流程实现安全设计。

UltraScale+ FPGAs & Zynq UltraScale+

Vivado Design Suite

- 面向 UltraScale+ 的隔离设计流程(IDF)规则/指南

XAPP1335“Zynq UltraScale+ 的隔离设计流程”主要介绍如何使用支持 Xilinx Vivado 设计套件的 Xilinx IDF 实现安全关键型设计。 - Vivado 隔离验证器用户指南 Vivado 隔离验证器用户指南

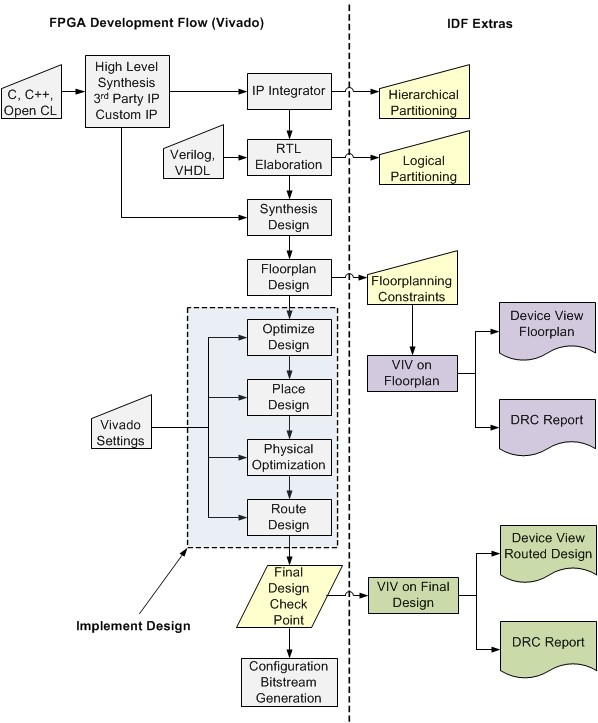

从 Vivado 2018.3 开始,Vivado 隔离验证器 (VIV) 将与 Vivado 版本集成,支持 UltraScale+ 器件(包括 Zynq UltraScale+)。本文档主要介绍如何在 FPGA/PL 设计中使用新的 Vivado 隔离验证器 (VIV) 来验证隔离。 - Zynq UltraScale+ 的隔离设计实例

Zynq UltraScale+ 的 XAPP1336 隔离设计实例

介绍如何将低功率域 (LPD) 作为一个通道和 PL 中的一个三模冗余 MicroBlaze 来创建和实现单片通用 2 通道系统。

验证工具

IDF 验证工具 (IVT and VIV) 验证 FPGA 设计划分为隔离区域,满足故障保险设计的严格标准。IVT 和 VIV 用于 FPGA 设计周期的两个阶段。IVT 先是用在设计流程早期,针对布局规划和引脚分配,执行一系列设计规则检查。设计完成后,再次使用IVT,所需隔离已置入设计。

隔离验证工具 (IVT) ISE Design Suite

IVT 为可执行文件,运行于 ISE 之外,但完全在 ISE 环境中。IVT 作为一组设计规则检查 (DRC) 运行,需要证明运行的设计是隔离的。它输出设计和详细文本报告的图形显示。

- IVT.zip 文件包含:

- IVT 可执行文件

- 版本说明和安装指南

- 许可协议

- 实验

注意: IVT 现有版本支持 、 Virtex-5、 Spartan-6、 和 7-系列 FPGA 和 SoC

- 下载 IVT 包 (ZIP)

Vivado 隔离验证 (VIV) Vivado Design Suite

VIV 是基于 Tcl 的脚本,集成 Vivado DRC 引擎。它本质上是一系列 DRC,加载到 Vivado - 执行证明设计隔离所需的所有检查。与 ISE 前身 IVT 不同的是,VIV 集成了利用 Vivado GUI 用户友好性的开发工具,但仍然保持独立的开发路径。其输出集成至 Vivado DRC GUI 显示以及由 Vivado DRC 引擎启动的文本输出

- VIV.zip 文件包含:

- VIV Script

- 版本说明和安装指南

- 许可协议

- Lab (即将推出)

注意: VIV 现有版本支持 Vivado 2015.1 或更高版本中的 7 系列 FPGA 和 SoC。

- 下载 VIV 包 (ZIP)

注意:从 2018.2 开始,Vivado 隔离验证器将与 Vivado 设计套件版本集成,而且这支持 UltraScale+ 器件(包括 Zynq UltraScale+)。了解更多信息,请参考 UG1291: Vivado Isolation Verifier 用户指南。