产品描述

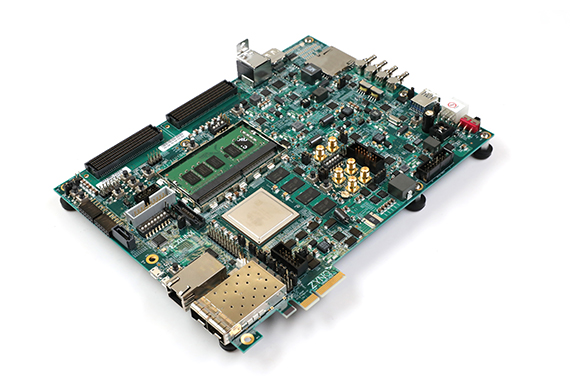

ZCU102 评估套件可帮助设计人员快速启动面向汽车、工业、视频以及通信应用的设计。该套件具有基于 Xilinx 16nm FinFET+ 可编程逻辑架构的 Zynq® UltraScale+™ MPSoC 器件,提供一款四核 ARM® Cortex®-A53、双核 Cortex-R5F 实时处理器以及一款 Mali™-400 MP2 图像处理单元。ZCU102 支持所有可实现各种应用开发的主要外设及接口。

主要性能和优势

- 经过优化,可采用 Zynq Ultrascale+ MPSoC 快速进行应用原型设计

- DDR4 SODIMM — 4GB 64 位、支持 ECC,与处理器子系统 (PS) 相连

- DDR4 组件 – 512MB 16 位,与可编程逻辑 (PL) 相连

- PCIe® 根端口 Gen2x4、USB3、显示端口与 SATA

- 4 个以太网 SFP+ 接口

- 两个用于 I/O 扩展的 FPGA 夹层卡 (FMC) 接口,包括 16 个 16.3Gb/s GTH 收发器和 64 个用户定义差分 I/O 信号

特色 Xilinx 器件

包含 Zynq UltraScale+ XCZU9EG-2FFVB1156 MPSoC

| 系统逻辑单元 (K) | 600 |

|---|---|

| 内存 (Mb) | 32.1 |

| DSP Slice | 2,520 |

| 最大 I/0 引脚 | 328 |

电路板特性

包含 ZCU102 评估板

配置

- 板上 JTAG 配置电路通过 USB 实现配置

- 双路 Quad-SPI 闪存

- 从 SD 卡启动

存储器

- PS 4GB DDR4 64-bit SODIMM w/ ECC

- 1200MHz / 2400Mbps DDR PL 512MB DDR4 组件内存 ([256 Mb x 16] 器件)

- 8KB IIC EEPROM

- 双 64MB Quad SPI 闪存

- SD 卡槽

控制 & I/O

- 6 个方向按钮 (5 个 PL、1 个 PS)

- DIP 开关 (8x PL)

- 面向电源、时钟、SD 卡和 I2C 总线切换的 PMBUS 及系统控制器 MSP430

- USB2/3 (MIO ULPI 和 1 GTR)**

扩展连接器

- 2 个 FMC-HPC 接插件 (16 个 GTH 收发器、 64 个差分用户定义信号)

- 2x PMOD 数据头

- IIC

通信与网络

- RGMII 的 10、100 或 1000 Mb/s 通信串行 GMII 接口 - 支持 1 Gb / s SGMII 接口

- 4x SFP+ cage

- SMA GTH 支持 (4 个 SMA Tx/Rx 接插件)

- UART 至 USB 的桥接器

- RJ45 以太网接插件

- SATA (1 x GTR)**

- PCIe Gen2x4 Root Port**

显示

- HDMI 视频输入输出 (3 GTH)

- 驱动 HDMI 输出接插件的外部重定时器器件

- 9 个 GPIO 用户 LED (8 个 PL、1 个 PS)

- VESA DisplayPort 1.2 数据源专用控制器在 1.62 Gb/s、2.70 Gb/s 或 5.40 Gb/s 下支持达两个通道的主链路数据。

时钟技术

- 可编程时钟

- 系统时钟、用户时钟, 抖动减弱时钟

- 2x SMA MGT 输入时钟

功耗

- 12V 插墙式适配器或 ATX

** 开关支持 PCIe 根端口 ,或支持 SATA、USB2/3 和 DisplayPort

特色 Xilinx 器件

包含 Zynq UltraScale+ XCZU9EG-2FFVB1156 MPSoC

| 系统逻辑单元 (K) | 600 |

|---|---|

| 内存 (Mb) | 32.1 |

| DSP Slice | 2,520 |

| 最大 I/0 引脚 | 328 |

内含物件

ZCU102 评估板

包含 Zynq UltraScale+ XCZU9EG-2FFVB1156 MPSoC

访问一整套 Vivado® Design Suite: Design Edition

节点锁定及器件锁定 XCZU9EG

以太网电缆

Targus USB-3

USB3 适配器

USB Micro 电缆

电源电线和适配器

访问 SDSoC 环境

使用 C, C++ 或 OpenCL 开发完整的 Zynq MPSoC 系统

合作伙伴

标题

日期

设计工具与下载

| 名称 | 说明 | 许可证类型 | 文件 |

|---|---|---|---|

| Vivado Design Suite | Xilinx Vivado® Design Suite 是一款以 IP 核及系统为中心的设计环境,这一全新构建的环境具有革新意义,能够显著加速 FPGA 和 SoC 系列器件的设计效率。 | XCZU9EG MPSoC FPGA 的锁定节点及锁定器件,1 年内可更新 | 下载 Vivado Design Suite |

| Vitis 统一软件平台 | 针对 Xilinx 平台提供全面的嵌入式软件开发、硬件加速及调试工具套件 | 免费 | 下载 Vitis 嵌入式平台 |

| PetaLinux 工具 | 将 Linux 操作系统配置、构建和部署至 Xilinx 平台。 | 免费 | 下载 Petalinux 工具 |

IP 核

| 名称 | 描述 | 许可证类型 |

|---|---|---|

| Memory Interface Generator (MIG) | 存储器接口发生器 (MIG) 是一款用于为赛灵思 FPGA 生成存储器控制器和接口的免费软件工具。 | 免费 IP |

其他工具、IP 和资源

| 名称 | 产品类别 | 项目 | 描述 |

|---|---|---|---|

| 开源 | 软件工具 | TeraTerm | 众多终端仿真器之一,用于实现 PC 与评估套件的串行连接。 |

| 功耗优势工具 | 软件工具 | 功耗优势工具 - Zynq UltraScale+ MPSoC | Power Advantage Tool 是一个演示工具,旨在展示 Zynq UltraScale + MPSoC 的电源特性。 |

| 深度学习 HDL Toolbox | 支持包 | MathWorks | 使用 MATLAB 在 Xilinx FPGA 和 SOC 上部署深度学习处理器 |

| 深度学习 HDL 工具箱入门指南 | 培训 |

MathWorks | 了解如何使用深度学习 HDL Toolbox™ 支持包创建、编译和部署 dlhdl.workflow 对象。 |

Default

Default

标题

日期