软件定义

注:自 2019.2 起,Xilinx SDKSDSoC™ 和 SDAccel™ 开发环境被整合为一个多用途的 Vitis™ 统一软件平台,用于应用加速和嵌入式软件开发。Xilinx SDAccel 开发环境将没有 2019.2 或更高版本。

简介

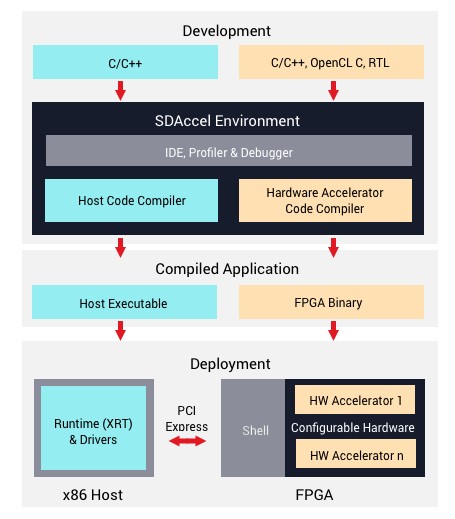

SDAccel™ 环境是一个集成型开发环境,主要针对面向 Xilinx Alveo 数据中心加速卡、AWS F1 实例以及其它 FPGA 即服务产品的应用。

它提供一个熟悉的软件开发流程,包括:

- 集成型开发环境 (IDE)

- 用于指导应用优化的分析器

- 面向主机及 FPGA 加速代码的编译器

- 快速开发及调试的仿真流程

- 软硬件间的自动通信

主机应用采用 C/C++ 开发,使用标准 OpenCL API 调用与 FPGA 加速函数互动,这些函数可以用 RTL 和 C/C++ 建模,也可以用 OpenCL 建模。这为硬件设计人员和软件工程师提供了熟悉的切入点。

SDAccel IDE 提供标准软件开发环境的所有特性:主机应用的优化编译器、灵活应变硬件的交叉编译器、稳健的调试环境,以及用于确定性能瓶颈问题及优化应用的分析器。

Xilinx 运行时 (XRT) 和开发板专用 shell 自动管理 FPGA 加速器和主机应用之间的通信。软件开发者无需执行任何这类连接细节。

优势

灵活应变硬件加速的优势

- 性能提高 10 至 1000 倍 *

- 低延时

- 功耗降低

- CPU 用时更短

- 易于使用 SDAccel 开发环境

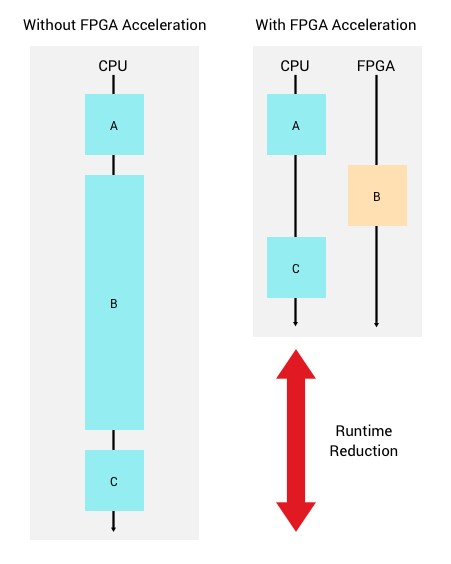

Xilinx FPGA 和 ACAP 器件特别适合对高性能算法及工作负载的低时延加速。

摩尔定律和登纳德缩放比例定律的下降,再加上 Amdahl 定律,这就意味着设计专用架构或 DSA 正在成为开发人员的首选工具,他们需要为他们的加速应用实现最高的性能、最短的时延以及最低的能耗。

FPGA 和 ACAP 器件非常灵活应变,与通用 CPU 和 GPU 截然不同,允许通过构建 DSA 来加速代码的特定部分。

SDAccel 开发环境提供一系列全面的工具报告,用于分析主机应用性能并确定加速机会。

这些工具还提供高速缓存、内存和总线使用的自动运行时检测,以跟踪硬件的实时性能。

* 性能提升从 10 到 1000 倍不等,主要取决于应用。

主要文档

SDAccel

面向 Alveo 的 SDAccel 许可

注意: 如果您已购买 Vivado HLx 许可,则您的帐户将拥有内部部署 AWS F1 开发的免费许可。

自发布 2018.2 XDF 起,所有 SDAccel 提供免费的 30 天试用。下载软件并在安装结束时选择免费试用版。