高层次设计

高层次设计功能

下面将概括介绍可加速高层次设计的 Vivado® ML 功能。点击其它标签,了解完整的特性详情。

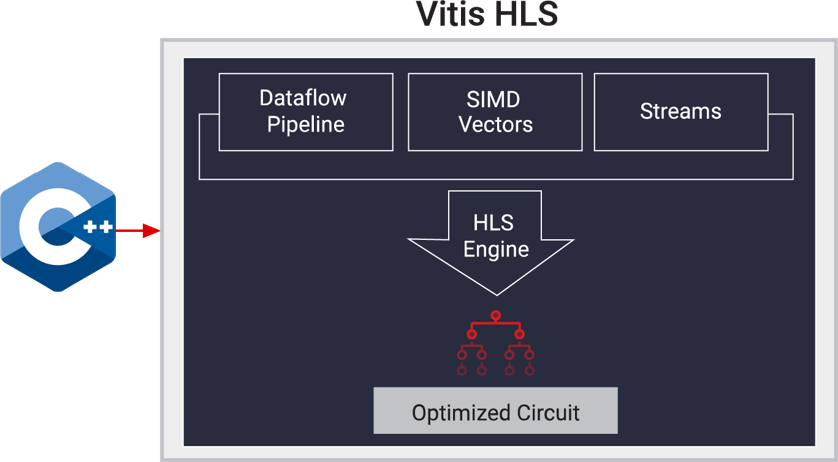

Vitis 高层次综合

当今 AI、无线、医疗、和消费类产品应用中使用的高级算法比以往更加复杂。Vivado® 高层次综合(HLS)在所有 Vivado HLx 版本中以免费升级形式提供,可以实现直接使用 C++ 规范对赛灵思可编程器件进行编程,无需手动创建等效的 RTL 设计,从而可加速 IP 创建。 同时支持 Vitis 和 Vivado 设计环境,Vitis HLS 通过以下方式为软件和硬件设计者提供了更快的内核或 IP 创建途径:

- 算法描述摘要、数据类型规格 (整数、定点或浮点) 以及接口 (FIFO, AXI4, AXI4-Lite, AXI4-Stream)

- 提供广泛的库,包括对任意精度数据类型、流和矢量化数据类型的内置支持

- 指令驱动型架构感知综合可提供最优的 QoR。

- 在竞争对手还在手动开发 RTL 的时候快速实现 QoR。

- 使用 C/C++ 测试平台仿真、自动 VHDL 或 Verilog 仿真和测试平台生成加速验证

- 自动使用 Xilinx 片上存储器、DSP元素,包括浮点类型

库

Vitis HLS 包含以下内置库:

| 名称 | 说明 |

|---|---|

任意精度的数据类型 |

整数和定点数(ap_int.h) |

HLS 流 |

面向流数据结构的模型。旨在实现最佳性能和面积 (hls_stream.h) |

向量类型 |

向量化类型和运算(hls_vector.h),包括任意精度类型 |

HLS Math |

广泛支持标准 C (math.h) 和 C++ (cmath.h) 数学库的综合。支持浮点和定点功能:abs, atan, atanf, atan2, atan2, ceil, ceilf, copysign, copysignf, cos, cosf, coshf, expf, fabs, fabsf, floorf, fmax, fmin, logf, fpclassify, isfinite, isinf, isnan, isnormal, log, log10, modf, modff, recip, recipf, round, rsqrt, rsqrtf, 1/sqrt, signbit, sin, sincos, sincosf, sinf, sinhf, sqrt, tan, tanf, trunc |

此外,Vitis 高层次综合工具还支持在 Github 上提供的 Vitis 性能优化库,只需对现有应用的代码进行细微修改,甚至无需修改,即可获得开箱即用的加速功能。这些常见的 Vitis 加速库包括数学、统计、线性代数和 DSP,可为各种应用提供各种核心功能。这些库可为支持 OpenCV 的视觉及图像处理、定量金融、数据库及数据分析以及数据压缩等工作负载提供开箱即用的加速功能。

IP Integrator

Vivado® ML 版可提供业界首款即插即用型 IP 集成设计环境并具有IP 集成器特性,从而解决了 RTL 设计生产力问题。

Vivado IP Integrator 可提供基于 Tcl、设计期正确的图形化设计开发流程。IPI 特性可提供具有器件和平台意识的互动环境,能支持关键 IP 接口的智能自动连接、一键式 IP 子系统生成、实时 DRC 和接口修改传递等功能,此外还提供强大的调试功能。

在 IP 之间建立连接时,设计人员工作在“接口”而不是“信号”的抽象层面上,从而大幅提升了生产力。 这通常采用业界标准的 AXI4 接口,不过 IP 集成器也支持数十个其它接口。

设计团队在接口层面上工作,能快速组装复杂系统,充分利用 Vivado HLS、Model Composer、Xilinx SmartCore™ 和 LogiCORE™ IP 创建的 IP、联盟成员 IP 和自己的 IP。通过利用 Vivado IPI 和 HLS 的完美组合,客户能将开发成本相对于采用 RTL 方式而言节约高达 15 倍。

Vivado IP Integrator 的主要特性和优势

- IP Integrator 层次化子系统在整个设计中的无缝整合

- 快速捕获与支持重复使用的 IP Integrator 设计封装

- 支持图形和基于 Tcl 的设计流程

- 快速仿真与多设计视窗间的交叉探测

- 支持处理器或无处理器设计

- 算法集成 (Vitis HLS 和 Model Composer) 和 RTL-level IP

- 融 DSP、 视、模拟、嵌入式、连接功能和逻辑为一体

- 支持基于项目的 DFX 流程

- 可在设计装配过程中,通过复杂接口层面连接实现 DRC

- 常见设计错误的识别和纠正

- 互联 IP 的自动 IP 参数传递

- 系统级优化

- 自动设计辅助

- 使用 Block Design Container 的基于团队的设计可实现可重用性和模块化设计

- 版本控制改进,将源文件与生成的文件分开

- 用于比较两个块设计的块设计差异工具

使用 Vitis 高层次综合和 Vitis Model Composer 生成基于 C 的 IP

作为可编程解决方案电子系统级设计工具的领先供应商,Vivado 提供适用于 C、C++ 和 SystemC 的 Vitis™ 高级综合,您可以购买用于 DSP 的附加 Vitis Model Composer。这些解决方案支持在 VHDL 和 Verilog 中直接综合高层次 IP 核规范,从而可将 IP 核验证速度提高 100 倍 以上,同时将 RTL 创建速度提高 4 倍。 您可以单独使用这些高度集成的工具,也可以综合结果分析,在 Vivado ML Suite 中使用可重用的 IP 核。

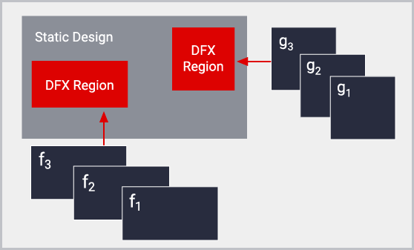

Dynamic Function eXchange (DFX)

Dynamic Function eXchange 可通过下载部分比特文件动态修改逻辑块,而其余逻辑将继续不间断运行。Xilinx DFX 技术允许设计者动态修改功能性,无需全面重配置和重构建链路,极大地增强了 FPGA 和 SoC 提供的灵活性;它是平台化设计流程的关键功能,对于 Alveo 加速卡而言,尤为明显。使用 Dynamic Function eXchange,有助于设计者转而采用更少或更小的器件,降低功耗并提高系统升级能力。随时按需加载功能,更有效利用芯片。

Dynamic Function eXchange 软件

Vivado® ML Design Suite 软件工具能够在不影响其它器件运行的前提下对 Xilinx FPGA 或 SoC 的部分功能进行重配置。目前的解决方案利用 Vivado ML Design Suite 骄人的实现功能,减少了创建可重新配置设计所需的开销。用户可以使用基于 Tcl 的非项目流程或基于 RTL 或 IP 的项目流程来实现设计。 IP Integrator (IPI) 设计支持是通过使用 Block Design Container 在 2021.1 版中引入的。Vivado IDE 支持 RTL 和 IP 项目模式,包含自动管理许多底层流程细节。设计流程的入口点包括通过 Vitis 和 HLS 处理的高级语言。高级流程功能,例如 Nested DFX,允许用户将动态区域细分为低阶动态区域,以及抽象外壳简化实现工具流程,大大提高运行时间,可在非项目模式下使用。

四项知识产权可帮助设计人员更快、更轻松地完成 DFX 设计。Dynamic Function eXchange 控制器是一款基于硬件的配置控制器,可帮助管理各个方面的重配置工作,从触发和仲裁到比特流交付和错误处理,无所不包。Dynamic Function eXchange 去耦器可以与 PR 控制器或任何客户控制器联用,在重新配置动态区时,可对其进行安全隔离。Dynamic Function eXchange AXI 关断管理器可帮助用户停止 AXI 接口上的活动,以便可重新配置分区能够安全地重新配置。{Dynamic Function eXchange 比特流监控器允许用户调试和监控部分比特流,以确保版本和目标的兼容性。

大多数 7 系列和 Zynq®-7000 器件都支持 Dynamic Function eXchange,唯一的例外是这些系列中最小的器件; 不支持某些 Artix-7 和所有 Spartan-7。UltraScale™ 支持非常完善,所有器件都可通过当前 Vivado Design Suite 版中的比特流生成获得支持。 UltraScale+™ 器件支持涵盖所有量产器件。在 Vivado 2021.1 中添加了量产型 Versal 支持。查看 DFX 可重配置用户指南 (UG909)、附录 A,了解最新信息。

UltraScale 代表了 Dynamic Function eXchange 技术的最新突破,支持几乎所有 FPGA 资源类型的重配置,包括 I/O、千兆位收发器和时钟网络等。UltraScale+ 通过优化比特流交付并扩展重配置模式,在这一功能强大的产品系列基础上做了改进。Versal 支持在效率方面取得了巨大的进步,最新支持基于软件的重新配置管理、可重新配置的片上网络、共享内存访问和布局规划粒度效率。

高校相关教授和研究人员可通过 Xilinx 大学计划 (XUP) 为较早版本的 Vivado 软件获取许可证。进一步了解有关获取许可证的访问要求和程序,请点击这里。

主要功能与优势

- Vivado IDE 中提供从 HDL 到比特流的 Tcl 非工程流程以及 RTL 和 IPI 工程模式

- 有效的数据库管理,面向静态和可重配置模块

- 支持黑箱比特流,允许省略不完整的模块

- 由用户决定如何管理可重配置的模块变量

- 保持静态设计在存储器中开放,并将模块调进调出

- 布局规划可确定对哪些资源进行重配置

- 工具可自动管理分区接口,没有任何开销

- 设计规则检查 (DRC) 可用于验证设计结构和配置情况

- 应用标准时序收敛技术

- 所有 Vivado® ML Design Suit 版本均免费提供 Dynamic Function eXchange。(从 2019.1 版起,Vivado WePack 版本自动包含其中。)

- 现已支持 Versal

- 并非包含 7 系列中的所有器件

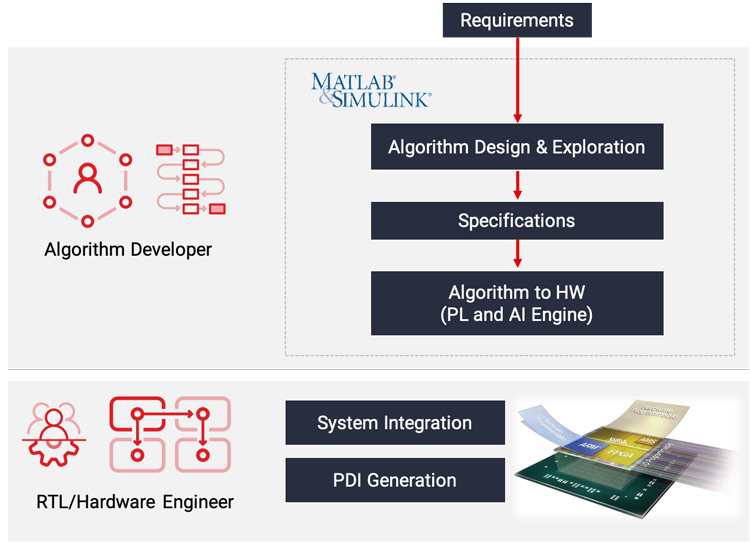

Vitis Model Composer

Vitis™ Model Composer 是一个基于模型的设计工具,不仅可在 MathWorks MATLAB® 和 Simulink® 环境中进行快速设计探索,而且还可通过自动代码生成在 Xilinx 器件上加速投产进程。您可以设计算法并使用高层次性能优化模块对其进行迭代,同时还可以通过系统级仿真验证功能正确性。Vitis Model Composer 可通过自动优化将您的设计转换为生产质量级实现方案。该工具提供一个具有 200 多个 HDL、HLS 和 AI 引擎模块的库,用于在 Xilinx 器件上设计并实现算法。此外,它还允许将自定义 HDL、HLS 和 AI 引擎代码按模块导入工具。Vitis Model Composer 包含用于 DSP 的 Xilinx 系统生成器的所有功能性,自 2020.2 版起,该系统生成器不再按独立工具发货。

在 Vitis Model Composer 中,您可以:

- 使用针对 AI 引擎和可编程逻辑的优化块,创建设计。

- 可视化仿真结果并对其进行分析,然后将得出的结果与使用 MALTAB® 和 Simulink® 生成的黄金参考进行比较。

- 无缝协同仿真 AI 引擎及可编程逻辑(HLS、HDL)模块。

- 自动生成代码(AI 引擎数据流程图、RTL、HLS C++)及设计测试台。

- 将自定义 HLS、AI 引擎和 RTL 代码作为模块导入。

主要特性

- 高层次抽象: 算法主导型构建块以功能性为重点,可为域专家提供至关重要的易用特性,以加速设计探索。

- 支持向量和矩阵: 可实现基于框架的算法设计,为您转而采用中间低层次实现模型节省宝贵的时间和精力。

- 应用专用库: 性能优化的 DSP、计算机视觉、数学和线性代数库可用作模块,在 Xilinx 器件上进行仿真和实现高性能。

- 将可综合的 C/C++ 导入为定制模块:能够创建您自己的仿真及代码生成模块,这可为设计差异化算法提供更大的灵活性。

- 与 Simulink 无缝集成: 与 Simulink 产品系列的模块直接连接,不仅可实现系统级建模和仿真,而且还能够充分利用 Simulink 图形环境的刺激生成和数据可视化功能。

- 支持整数、浮点和定点支持: 支持 Simulink 中的原生浮动和整数数据类型,以及由 Vivado HLS 提供支持的定点和半数据类型。

- 自动优化: 不仅可分析 Simulink 中的算法规范和执行自动优化,以实现可针对吞吐量进行优化的微架构,而且还可降低 Block RAM 利用率并实现模块的并行执行。

- 加快 IP 创建: 将支持仿真的设计变成您可在 Vivado IP Integrator 中使用的 RTL IP 封装并充分利用复杂设计即插即用 IP 集成设计环境的所有优势。

- 扩展至 System Generator for DSP: 利用 Model Composer 易用性及仿真速度的优势,运用到设计的各部分并将合成的 RTL 导出到您现有的 System Generator for DSP 设计中作为新的自定义模块。

- 导出至 Vitis HLS:高级特性可通过自动生成您进一步优化算法将需要的一切(包括从仿真中记录的测试向量)在设计、仿真和验证您设计的 Simulink 图形环境与 Vivado HLS 之间提供一条链路。

- 使用界面映射 RTL 接口: 可便捷地使用图形界面将设计中的输入和输出映射至所支持的 RTL 接口(AXI4-Lite、AXI4-Stream、AXI4-Stream 视频、FIFO 和 Block RAM)以及用于实现方案的视频格式(AXI4-Stream 视频)。

- 自动测试工作台生成: 对来自测试工作台仿真和生成的测试向量自动生成日志,以验证可执行设计和所生成代码之间的功能对等值。