验证

验证

下面将概括介绍 Vivado ML 的验证特性。点击其它标签,了解完整的特性详情。

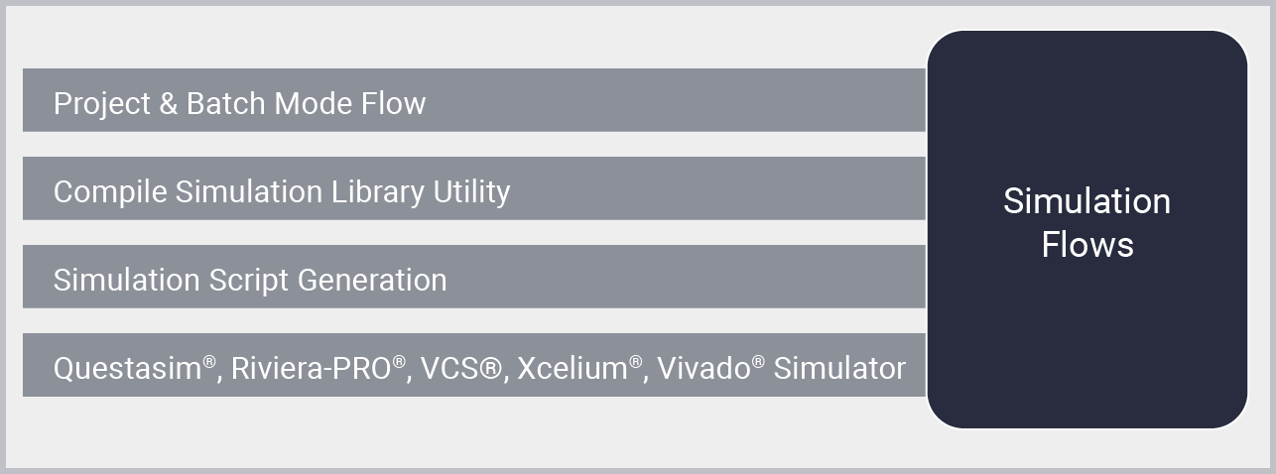

仿真流

Vivado® Design Suite 可为单个业界一流集成设计环境 (IDE) 中所包含的第三方仿真器提供设计入口、时序分析、硬件调试以及仿真等一系列功能。对于所有所支持的仿真器而言,该流程都可满足集成型及企业验证需求。

Vivado 可为全面集成型 Vivado Simulator以及第三方 HDL 仿真器实现行为、后期综合与后期实现功能或时序仿真。设计周期早期阶段多花点时间在仿真上,有助于提早识别问题,相对于在流程后期阶段多用时间而言,可显著减少转换时间。

为帮助在用户验证环境中实现高灵活性,Vivado 不仅提供对集成环境的支持,而且还提供各种脚本与外部验证设置联用。

Vivado IDE 支持所有主流仿真器,无论是在交互式仿真用户的集成模式下还是在高级验证工程师的脚本模式下,都没有问题。

Aldec — Active-HDL® 与 Riviera-PRO®、Cadence Xcelium® 仿真器、Siemens EDA — ModelSim® 与 Questasim®、Synopsys VCS® 以及 Xilinx Vivado 仿真

主要特性

- 仿真流程助力在用户环境中为所支持的仿真器编译仿真库,从而可实现对编译库的重复使用。

- 能够在设计过程的不同阶段仿真和验证设计完整性,如行为、综合后功能及时序仿真以及实现后功能及时序仿真等。

- 对所有模拟器使用一致的 3 步流程(编译、精心设计、模拟)进行统一模拟集成

- 为第三方企业仿真器生成仿真脚本,以便通过用户自己的环境执行验证。

Vivado 仿真器

Vivado® 仿真器是一款具有丰富功能的多语言仿真器,支持 Verilog、SystemVerilog 和 VHDL 语言。随附提供的 Vivado 仿真器是 Vivado 的重要组成部分,无需支付额外的费用。它没有设计尺寸、实例或线路限制,可使用单个 Vivado 许可证运行无限的混合语言仿真实例。

Vivado 仿真器支持 Windows® 和 Linux 操作系统,可提供强大的调试特性,充分满足 Xilinx 客户的验证需求。

Vivado 仿真器是硬件描述语言 (HDL) 事件驱动的仿真器,支持单一语言及混合语言设计的行为与时序仿真。

主要特性

- SystemVerilog (包括约束随机化和功能覆盖)

- Verilog 2001

- VHDL 93 和 VHDL 2008

- 高级波形查看器,可查看数字/模拟波形及事务处理

- 断点、子程序调试和交叉探测等综合调试工具

- 支持 UVM 1.2 库

- 功能覆盖范围

- 支持 GUI 和脚本模式

- 直接编程接口 (DPI)

- Xilinx 仿真接口 (XSI)

编程和调试

Vivado® Debug 提供多种解决方案来帮助用户更高效便捷地调试其设计。这些解决方案包含各种工具、IP 和流程,支持从逻辑到系统级调试的各种功能,而且用户设计在硬件中运行。

此外,Vivado 还提供统一的设计环境,您可以在相同的 IDE 中执行不同的调试任务。在该 IDE 中,界面的外观一致,各种功能彼此通信良好。

亮点

作为 Vivado IDE 的一部分,硬件管理器可帮助用户编程器件并在比特流生成后调试设计。使用硬件管理器,用户可连接并编程包含一个或多个 FPGA 器件的硬件目标,然后可通过 Tcl 或 GUI 接口与调试 IP 互动,包括逻辑分析器、串行 I/O 分析器以及存储器校准调试。

- 面向 FPGA、配置存储器器件、eFUSE AES 键/寄存器的器件编程器

- Tcl 脚本编写支持调试自动化

- 通过 hw_server 和 Xilinx 虚拟线缆对网络进行远程调试 (XVC)

Vivado 提供各种调试 IP 和工具特性,可帮助您为您所实现的设计轻松执行系统内逻辑调试。

- ILA — 用于触发事件并捕获内部信号数据

- System ILA — 用于为 AXI 接口执行事务处理级调试

- VIO — 用于监控并驱动内部信号

- JTAG - AXI — 用于通过 Tcl 直接与 AXI 接口交互

Vivado 可为您提供一个快捷的方法来调试和优化 FPGA 收发器。该解决方案包括一个可定制的调试 IP (IBERT) 和 Vivado 串行 I/O 分析工具。如果结合使用,您可对多个通道进行误码率 (BER) 测量,执行 1D/2D 眼图扫描,实时调整收发器参数,而您的串行 I/O 通道还能够与系统其它部分进行互动。

此外,IBERT 还包括数据模式生成器和检查器,支持对收发器 DRP 端口的访问,可用于 PMA 评估和收发器演示。当在 FPGA 中实现了 IBERT 后,Vivado 串行 I/O 分析器不仅可与 IP 互动,而且还允许您创建链路(类似于开发板上的通道),并可通过以图形方式运行扫描和查看结果来分析链路的裕量。

内存校准调试工具允许您快速调试内存接口(DDR4/3、RLDRAM3、QDRII+ 和 LPDDR3)中的校准或数据错误。您一直可在工作的整个过程中随时查看和分析硬件中存储器接口的内核配置、校准状态和数据裕量。

Xilinx 虚拟线缆 (XVC) 解决方案是一种基于 TCP/IP 的协议,类似于 JTAG 线缆,可提供一种无需使用物理线缆便可访问和调试 FPGA 或 SoC 设计的方法。XVC 解决方案具有软件及硬件组件:

ChipScopy 是一款 Python API,只允许针对 Versal 器件进行器件编程、通信与调试。高层次 Python 函数支持 TCF 服务器连接、器件编程、读写内存、触发和捕获 ILA 数据以及读写 VIO 寄存器。此外,它还支持运行 IBERT 扫描、读取系统监控数据、监控 NOC 性能、报告 DDR 指标。

Verification IP

Xilinx Verification IP (VIP) 产品组合使您可在仿真环境中更轻松、快捷和高效地验证和调试设计。Verification IP 核是一种特定构建的验证模型,旨在确保正确的互操作性和系统运行。EDA 行业的公司正在为基于标准的接口(AXI、PCIe、SAS、SATA、USB、HDMI、ENET 等)开发 VIP。使用 VIP 的优势包括提升设计质量以及通过重复使用缩短时间周期等。

Xilinx VIP 内核是基于 SystemVerilog 的仿真模型,可通过 ARM 许可的断言提供全面的 AXI 协议检查,并支持所有主要仿真器,它是 Vivado 附带的免费内核。Xilinx 提供的 VIP 可用于使用 AXI 组件层次(AXI-MM、AXI_Stream)和处理系统 (Zynq®-7000) 的设计。

主要特性

- AXI4、AXI4-Stream 和 AXI4-Lite 的 AXI 流量生成器

- 全面支持 AXI & AXI Stream 协议检查器

- 为基于 Zynq-7000 和 Zynq US+ MPSoC 的应用提供功能仿真支持

- 支持控制、接口和处理系统 (CIPS) IP 的功能仿真