Versal AI Prime 系列

Versal Prime 系列提供一系列不同的计算引擎、新一代 I/O 和集成型 DDR 控制器,可在各种工作负载下实现低时延加速。

针对连接、内联加速以及不同工作负载进行了优化

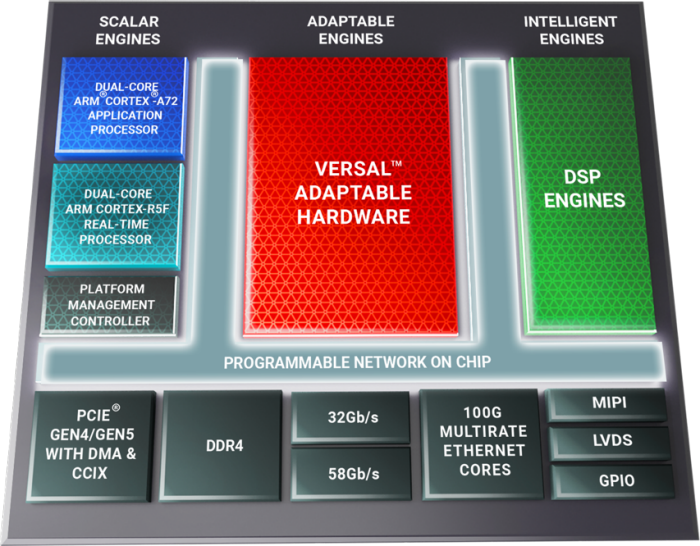

标量引擎

Versal™ ACAP 中提供了三种标量处理器类型,可支持各种应用需求。应用处理单元非常适合操作系统支持的复杂应用,实时处理单元非常适合需要低时延、确定性以及实时控制的应用。一款单独的平台管理控制器管理系统启动、安全性与调试。

自适应引擎

可编程逻辑可实现为不断变化的算法开发自定义计算模块。Versal ACAP 中重新架构的逻辑可为每个 CLB 提供 4 倍的密度,从而可减少对高成本全局路由的需要。这些灵活应变的引擎加载了各种广泛的内存元件,并与可编程 I/O 紧密耦合,允许用户为任何应用创建强大的加速器。

智能引擎

增强的 DSP 引擎可为最新工作及数据类型提供支持,包括统一半精度浮点运算以及复杂的 18x18 工作。有了对 UltraScale+™ 设计的向后兼容性,用户可不断利用现有的库和 IP 或更新他们的设计,来获得这种新架构带来的更高计算性能。

下一代 I/O

Versal Prime 系列将 PCIe® Gen4/Gen5 合规性、CCIX 支持、高性能 GPIO 以及支持各种以太网配置的多速率以太网 MAC 进行完美结合,可最大限度提高连接性和灵活性。此外,Versal Prime 系列器件还具有重新架构的低时延 32.75Gb/s 的收发器,而且某些器件还支持 58Gb/s 的 PAM4 收发器。

集成型 DDR 内存控制器

每款集成型 DDR 内存控制器不仅提供高达 34.1Gb/s 的带宽,支持 DDR4 和 LPDDR4,而且还针对线性及随机流量进行了优化。这些集成型控制器与片上可编程网络相结合,无需在可编程逻辑中进行软实现,从而可节省开发时间和逻辑资源。

可编程的片上网络

可编程片上网络 (NoC) 在 Versal ACAP 架构中的不同计算引擎与集成 IP 模块之间提供了优化的多兆位互连,从而简化了时序收敛并节省了逻辑资源。NoC 编译器不仅提供优化的编程体验,同时还允许用户管理时延和 QoS,可确保关键数据路径为优先级。

Versal™ Prime 系列支持高性能和高灵活性,可解决广泛的特定行业问题

存储加速

随着人工智能的出现以及现代应用所生成数据的激增,传统计算已经成为数据中心越来越宝贵的资源。保存计算的一个解决方案是在存储控制器和端点中添加加速器,以卸载主处理器的压缩以及其它常见任务。Versal Prime 系列将 PCIe® Gen4/Gen5 支持、强大的 Arm® 标量处理引擎、集成型内存控制器以及新一代可编程逻辑相结合,不仅可减少系统级瓶颈问题,而且还可提高效率。

数据中心网络加速

FPGA 和 SoC 长期以来一直在加速数据中心应用中发挥着重要作用,它们可卸载系统中中央处理器的加密/解密以及虚拟交换等常见网络功能,从而可保存计算周期。Versal ACAP 通过将 PCIe Gen4/Gen5 支持、新一代 SerDes 和多速率以太网 MAC 与强大的异构计算引擎相结合,进一步加速数据中心系统,以减轻网络运算的负载,并通过额外的内联处理来补充服务器中可用的计算。

5G xHaul

随着 5G 的出现,对高带宽连接的需求要求接入网络,才能在适应支持 eCPRI 等新协议的同时,仍保持与现有标准的兼容。在 Versal Prime 系列中将灵活应变的引擎与行业领先的串行解串器和以太网技术相结合,不仅可为运营商提供处理 5G 吞吐量需求所需的处理能力,同时还可维护对原有标准的支持,并降低总体拥有成本。

无源光网

随着无线服务竞争的加剧,有线宽带提供商必须扩展其网络并提供更高的带宽服务,才能保持竞争力。Versal Prime 系列提供比现有 MPSoC 器件高 1 倍的可编程逻辑、强大的 Arm 标量处理引擎、更高的串行解串器密度、集成型以太网 IP 块以及散热优化封装,可在不影响性能的情况下,实现低功耗的高效设计。

通信测试设备

伴随最新通信标准的带宽爆炸式增长,使测试设备厂商很难跟上市场需求的发展步伐。Versal Prime 系列产品支持 58G 收发器和多速率以太网 MAC,可为有线通信测试人员提供高性能的数据处理和分析。可编程 NoC 和集成型内存控制器可为复杂的测试算法实现快速高效的数据移动。

Versal Prime 系列特性概览

标量引擎功能

| VM1102 | VM1302 | VM1402 | VM1502 | VM1802 | VM2202 | VM2302 | VM2502 | VM2902 | |

|---|---|---|---|---|---|---|---|---|---|

| 应用处理单元 | 双核 Arm® Cortex -A72、48KB/32KB L1 高速缓存支持奇偶校验和 ECC,1MB L2 高速缓存支持 ECC | ||||||||

| 实时处理单元 | 双核 Arm® Cortex -R5F、32KB/32KB L1 高速缓存以及支持 ECC 的 256KB TCM | ||||||||

| 存储器 | 支持 ECC 的 256KB 片上内存 | ||||||||

| 连接功能 | 以太网 (x2)、USB 2.0 (x1)、UART (x2)、SPI (x2)、I2C (x2)、CAN-FD (x2) | ||||||||

智能引擎功能

| VM1102 | VM1302 | VM1402 | VM1502 | VM1802 | VM2202 | VM2302 | VM2502 | VM2902 | |

|---|---|---|---|---|---|---|---|---|---|

| DSP 引擎 | 464 | 832 | 1,696 | 1,312 | 1,968 | 1,312 | 1,904 |

3,984 | 2,672 |

灵活应变的引擎功能

| VM1102 | VM1302 | VM1402 | VM1502 | VM1802 | VM2202 | VM2302 | VM2502 | VM2902 | |

|---|---|---|---|---|---|---|---|---|---|

| 系统逻辑单元 (K) | 329 | 693 | 1,238 | 981 |

1,968 | 1,139 | 1,575 | 1,969 | 2,233 |

| LUT 数 | 150,272 | 316,928 | 565,760 | 448,512 |

899,840 | 520,704 | 719,872 | 900,224 | 1,020,928 |

基础平台功能

| VM1102 | VM1302 | VM1402 | VM1502 | VM1802 | VM2202 | VM2302 | VM2502 | VM2902 | |

|---|---|---|---|---|---|---|---|---|---|

| NoC 主 / NoC 从端口 | 5 | 9 | 18 | 21 |

28 | 21 | 30 | 28 |

42 |

| DDR 内存控制器 | 1 | 2 | 4 | 3 |

4 | 3 | 3 |

4 |

3 |

| CCIX & PCIe® (带有 DMA) (CPM) | - | 1 x Gen4x16、CCIX | 1 x Gen4x16、CCIX | 1 x Gen4x16、CCIX | 1 x Gen4x16、CCIX | 2 x Gen5x8, CCIX | - |

2 x Gen5x8, CCIX | - |

| PCIe | 1 x Gen4x8 | 2 x Gen4x8 | 2 x Gen4x8 | 4 x Gen4x8 | 4 x Gen4x8 | 4 x Gen5x4 | 2 x Gen5x4 | 2 x Gen5x4 | 2 x Gen5x4 |

| 多速率以太网 MAC | 1 | 2 | 2 | 4 | 4 | 2 | 6 | 2 | 6 |

| 32Gb/s GTY 收发器 | 0 | 24 | 24 | 44 | 44 | 0 | 0 | 0 | 0 |

| 32Gb/s GTYP 收发器 | 8 |

0 | 0 | 0 | 0 | 32 | 8 |

28 |

8 |

| 58Gb/s GTM 收发器 | 0 |

0 |

0 |

0 |

0 |

0 | 40 | 16 | 40 |

技术文档

搜索文档

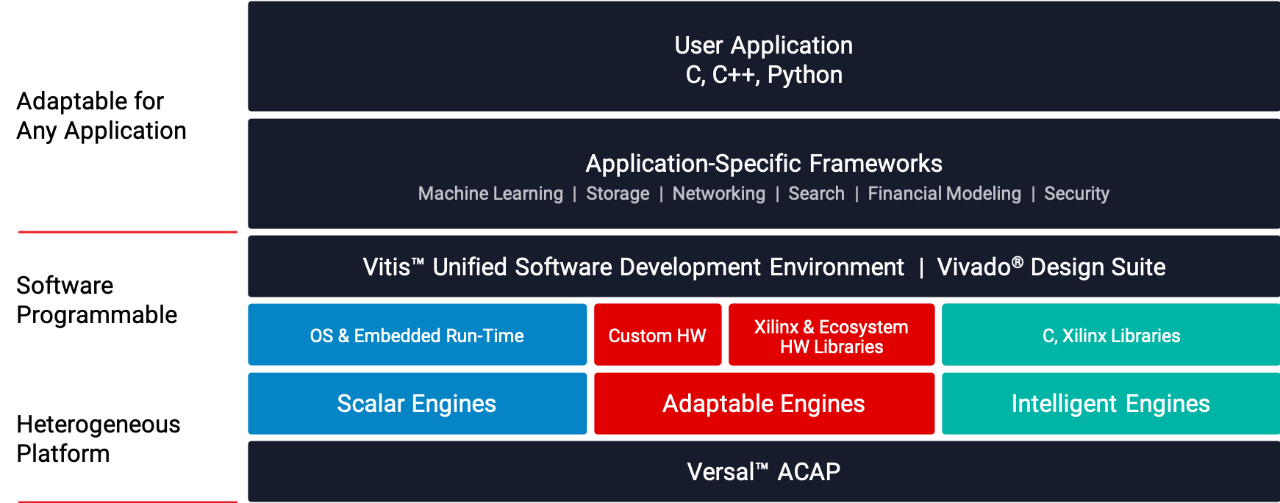

面向所有开发者的集成型软硬件平台

Versal™ ACAP 采用固有的软件可编程芯片基础架构,其设计自始至终都是以软件为导向的。增强型 Xilinx® Vivado® Design Suite 引入全新系统设计方法和开发环境,如流量分析仪、NoC 编译器和数据流建模等。一个紧密结合的高速、统一调试环境可加速跨灵活应变的标量智能引擎的调试与跟踪。

下载 Vivado Design Suite >

Xilinx Vitis™ 统一软件平台提供了全面的核开发套件,以及使用硬件加速技术的库。该平台提供从云端到边缘的高效、便捷、统一的软件环境。作为开源社区的重要成员,Vitis 统一软件平台是完全免费和开源的。

下载 Vitis™ 统一软件平台 >

Versal ACAP 评估套件

欢迎率先体验 Versal ACAP 架构,从头开始构建,实现原生的软件可编程性。通过一系列工具、软件、库、IP、中间件和固件,ACAP 可通过业界标准设计流程实现各种定制化的加速计算解决方案。Versal Prime 系列 VMK180 评估套件拥有快速启动设计所需的所有组件。

培训课程

Xilinx 培训和学习资源提供了实用的实践技能和基础知识,可助力开发者在下一个开发项目中充分发挥生产力。

使用 Xilinx Versal ACAP 平台开启设计

使用 Versal ACAP 进行设计:架构和方法

使用 Versal ACAP 进行设计:可编程片上网络

使用 Versal ACAP 进行设计 - 电源和开发板设计