AR# 37472

|Design Assistant for PCI Express - How to read packets on the Integrated Block for PCI Express's memory (or MIM) interface

描述

This Answer Record describes how to read packets on the PCI Express Integrated Block's memory interface.NOTE: This Answer Record is part of the Xilinx Solution Center for PCI Express (Xilinx Answer 34536). The Xilinx Solution Center for PCI Express is available to address all questions related to PCIe. Whether you are starting a new design with PCIe or troubleshooting a problem, use the Solution Center for PCIe to guide you to the right information.

解决方案

All TLPs pass through the memory or MIM interface.The MIM interface consists of two sets of dual ported BRAMs. One set is for the transmit side and the other is for the receive side. The amount of BRAM used depends on the core and options you chose for the core. The BRAM is part of the FPGA fabric and is not within the integrated block. For this reason, you can interpret TLPs as they flow into and out of the BRAM in the interfaces listed below:

The TX side has the following signals:

MIMTXWEN

MIMTXWADDR

MIMTXWDATA

MIMTXREN

MIMTXRADDR

MIMTXRDATA

The RX side has the following signals:

MIMRXWEN

MIMRXWADDR

MIMRXWDATA

MIMRXREN

MIMRXRADDR

MIMRXRDATA

The "W" and the "R" in the names indicate "write" and "read," respectively.

The "EN" in the names indicates an enable for the BRAM.

The "ADDR" in the names indicates the address of the BRAM.

The "DATA" in the names indicates the data in the BRAM that is being read from or written to.

The "DATA" bus will contain the TLP.

The DATA and ADDR on the "write" side of the BRAM will be aligned to the "WEN" signal.

The DATA on the "read" side of the BRAM will come out of the BRAM two clock cycles after the "REN" signal.

Depending on the device, there may be additional bits appended to the MIM***DATA bus. The bits that are appended can be ignored. The valid TLP data on the MIM***DATA bus will always be either 1DW or 2DW. The upper bits resulting in a greater than 1 or 2 DW length can be ignored.

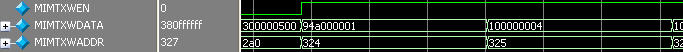

The figure below shows a Completion with Data of 1 DW on the transmit MIM interface. There data width is 64 bits or 2 DW with no extra bits appended.

The figure below shows a Completion with Data of 1 DW on the transmit MIM interface. The data width is 64 bits or 2 DW with 4 extra bits appended. The '9' at address x324 should be ignored and the 1 at address x325 should be ignored.

By default, the MIM interface acts as a fill-and-spill interface. This means that an entire TLP is written to the MIM interface before it is read from. Virtex-6 and Spartan-6 FPGA allow you to improve the latencyby using the streaming mode (cut-through) feature on the transmit interface. Instreaming mode, theintegrated blockstarts reading the TLP out of the BRAM and sendingit on to the link before the user finishes transmitting the full packet into the BRAM.For more information on streaming mode, please refer to the appropriate user guide(Xilinx Answer 35920).

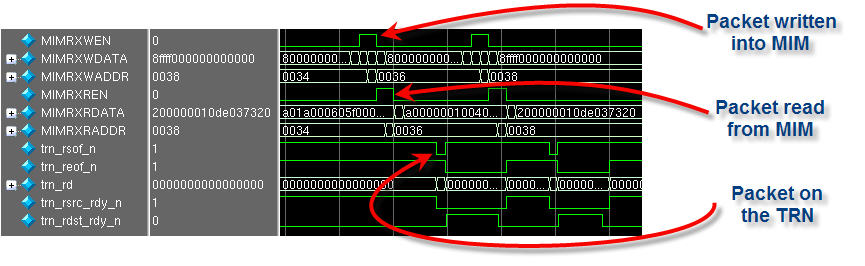

The figure below shows the flow of a packet going through our receiving MIM interface and ending up at the TRN interface.

The figure below shows the flow of a packet being transmitted from the TRN interface and going through the transmit MIM interface.

Revision History:

11/19/2010 - Initial Release

本答复记录是否对您有帮助?

链接问答记录

相关答复记录

| Answer Number | 问答标题 | 问题版本 | 已解决问题的版本 |

|---|---|---|---|

| 34538 | Xilinx Solution Center for PCI Express - Design Assistant | N/A | N/A |

| AR# 37472 | |

|---|---|

| 日期 | 02/28/2013 |

| 状态 | Active |

| Type | 综合文章 |

| IP | |

People Also Viewed