AR# 43521

|MIG Spartan-6 MCB - General Board Level Debug

描述

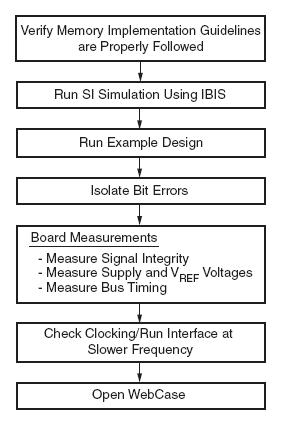

This Answer Record provides information on general board level debug for MCB designs using MIG.The information provided in this Answer Record should be the starting point in any hardware debug of a memory interface design.

NOTE: This Answer Record is part of the Xilinx MIG Solution Center (Xilinx Answer 34243). The Xilinx MIG Solution Center is available to address all questions related to MIG. Whether you are starting a new design with MIG or troubleshooting a problem, use the MIG Solution Center to guide you to the right information.

解决方案

Following is the recommended flow for debugging a hardware issue involving a memory interface:For detailed information on Verify Memory Implementation Guidelines, refer to:

- (Xilinx Answer 40775) Board Layout

- (Xilinx Answer 43318) Verify Pin-out Requirements

Each of these steps is detailed in the Debug Guide provided withSpartan-6 FPGA Memory Interface Solutions User Guide (UG416); see the Debugging MCB Designs section:http://www.xilinx.com/support/documentation/ip_documentation/mig/v3_8/ug416.pdf

To open a WebCase, go to:

http://www.xilinx.com/support/clearexpress/websupport.htm

链接问答记录

相关答复记录

| Answer Number | 问答标题 | 问题版本 | 已解决问题的版本 |

|---|---|---|---|

| 43520 | MIG Spartan-6 MCB - Board Debug (including general, calibration, and data error debug) | N/A | N/A |

| AR# 43521 | |

|---|---|

| 日期 | 12/15/2012 |

| 状态 | Active |

| Type | 综合文章 |

| 器件 | |

| IP | |