AR# 44094

|MIG Spartan-6 FPGA DDR2/DDR3 - How do I drive the user interface?

描述

This part of the MIG Design Assistant will guide you to information on driving the User Interface.NOTE: This Answer Record is a part of the Xilinx MIG Solution Center (Xilinx Answer 34243). The Xilinx MIG Solution Center is available to address all questions related to MIG. Whether you are starting a new design with MIG or troubleshooting a problem, use the MIG Solution Center to guide you to the right information.

解决方案

Interfacing to the Core

The User Interface resembles a simple FIFO interface.

User Interface

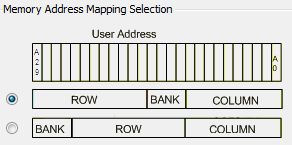

The nextdiagram shows the physical abstraction for theBANK, ROW, and COLUMN address scheme that the User Interface uses. This allows for a simple logical address interface.You can choose to select theBANK ROW COLUMN and ROW BANK COLUMN for optimal performance within the MIG tool.

Command Path

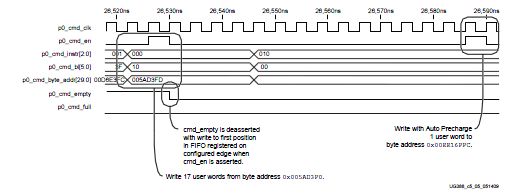

The User Interface (UI) loadsa command to the FIFO command when both the user logicpX_cmd_en is asserted and pX_cmd_full is not asserted from the UI. The user logic must hold thecmd_en high one cycle with the valid command, burst length, andaddress value.

The next diagram shows a Write command example.

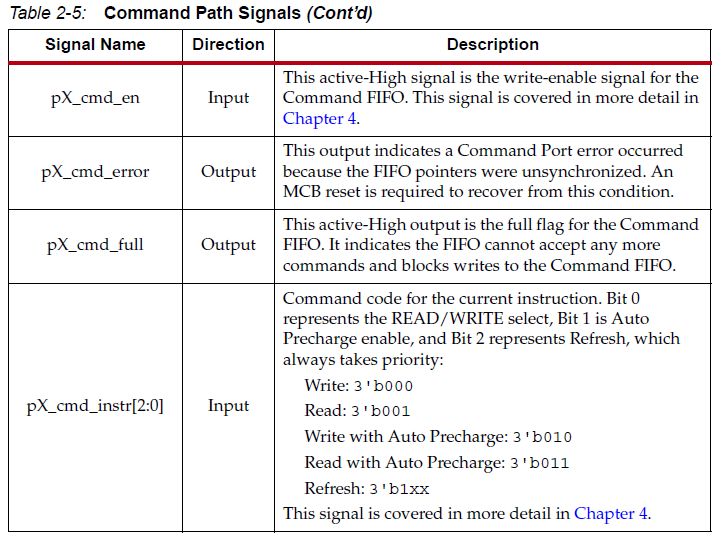

Available commands on the pX_cmd port are as follows:

You can issue the Refreshcommand by yourself, however, the core performs anauto-refresh of the memory at regular intervals and this cannot be disabled.

For more details on sending specific commands and the addressing scheme, pleasesee the following:(Xilinx Answer 43356) - Performing Reads

(Xilinx Answer 43355) - Performing Writes

(Xilinx Answer 43360) - Addressing

(Xilinx Answer 43358) - Masking Data

(Xilinx Answer 34154) - Refresh

For additional information, please refer to the UG416and UG388.

链接问答记录

主要问答记录

| Answer Number | 问答标题 | 问题版本 | 已解决问题的版本 |

|---|---|---|---|

| 37496 | Xilinx Spartan-6 MIG Solution Center - Design Assistant | N/A | N/A |

相关答复记录

| Answer Number | 问答标题 | 问题版本 | 已解决问题的版本 |

|---|---|---|---|

| 44320 | MIG Spartan-6 FPGA DDR2/DDR3 - User Design Usage | N/A | N/A |

| 43360 | MIG Spartan-6 MCB 用户接口 – 寻址 | N/A | N/A |

| 43358 | MIG Spartan-6 MCB - Masking Data with the User Interface | N/A | N/A |

| 43356 | MIG Spartan-6 MCB- User Interface - Performing Reads | N/A | N/A |

| 43355 | MIG Spartan-6 MCB - User Interface - Performing Writes | N/A | N/A |

| AR# 44094 | |

|---|---|

| 日期 | 02/25/2013 |

| 状态 | Active |

| Type | 综合文章 |

| 器件 | |

| IP | |