AR# 56113

|Spartan-6 BUFIO2, DIVIDE 设计咨询= 第 2 版

描述

在 Spartan-6 FPGA 中,使用 DIVIDE(2) 应用的 BUFIO2 偶尔会进入 stuck 状态。因此,不支持该器件,需要采用另一种实现方案。

解决方案

当处于 stuck 状态时,DIVCLK 和 SERDESSTROBE 输出不会运行。BUFIO2 直到重新配置前,始终会保持 stuck 状态。IOCLK 不依赖于状态机,同时会继续运行。

在某些配置下,BUFIO2 因为时钟输入glitches而进入 stuck 状态。产生这类glitches的原因有多种,包括:时钟不稳定、浮动输入或 FPGA 配置启动情况。即使 Spartan-6 器件输入端为已知时钟,BUFIO2 仍然可能因为 FPGA 配置或启动条件中的内部故障而进入 stuck 状态。

DRC 信息

如果使用 DIVIDE = 2(从 ISE 设计套件 14.6 开始提供),你将看到如下 DRC 错误:Element BUFIO2_XY has invalid setting of divide by 2。不支持该设置。如需了解更多信息,敬请查看 (Xilinx 答复 56113)。

上述 DRC 错误将在 ISE 设计套件 14.6 中出现。

替代方案

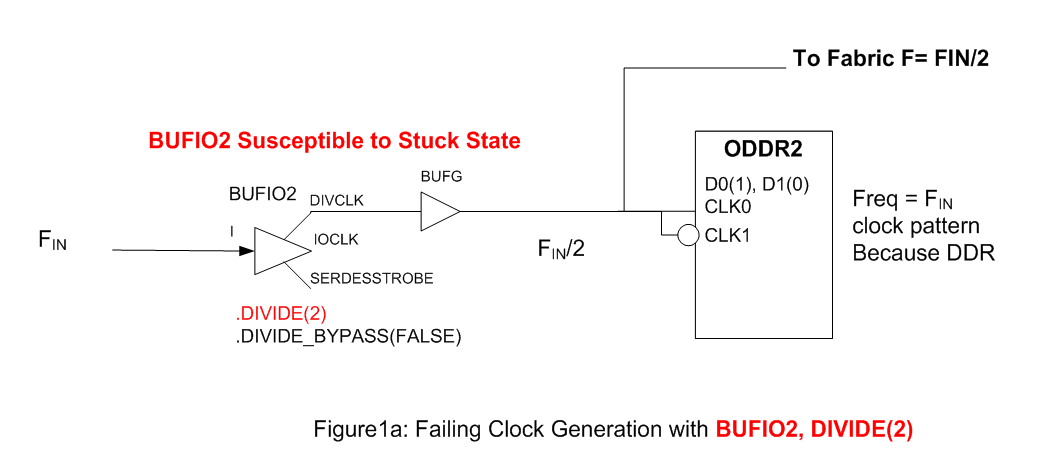

为了避免使用 BUFIO2、DIVIDE(2) 设置,这里列举了一些降低时钟频率的标准方法。这肯定不是完整列表,但可用来强调一些常见解决方案。在图 1a:“利用 BUFIO2、DIVIDE(2) 实现的错误时钟生成方法”中,BUFIO2 用 2 除以 FIN。

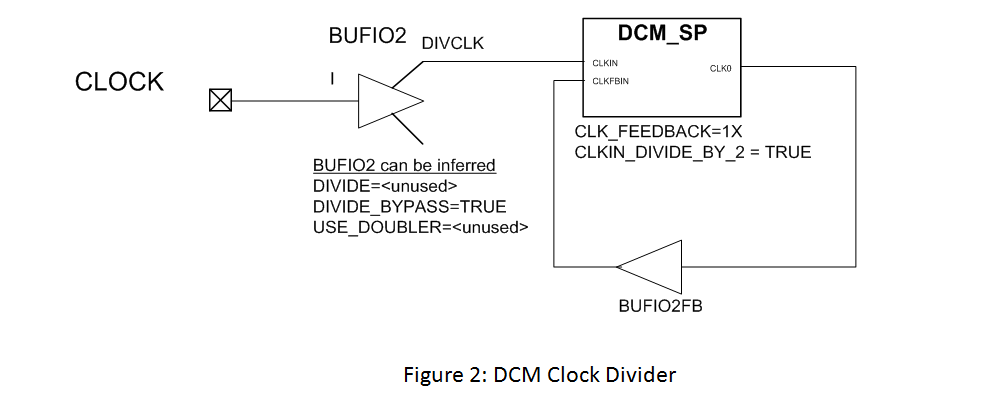

通常使用 DCM 和 PLL 来除 FPGA 的内部时钟;这些技术仍然适用,而且可用于避免错误的 BUFIO2 条件。 请记住 DCM/PLL 要求必须得到满足。如果设计包含相位对齐要求,那么需要像 DCM 时钟分频器中那样额外使用 BUFIO2FB 反馈缓冲器。类似地可以使用 PLL。

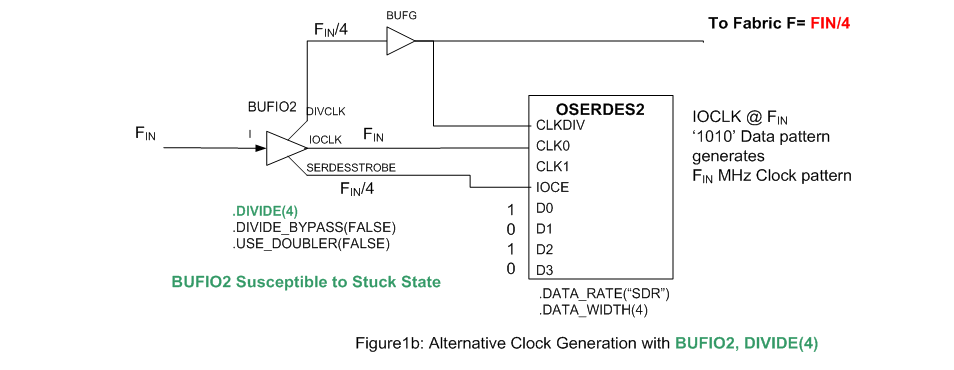

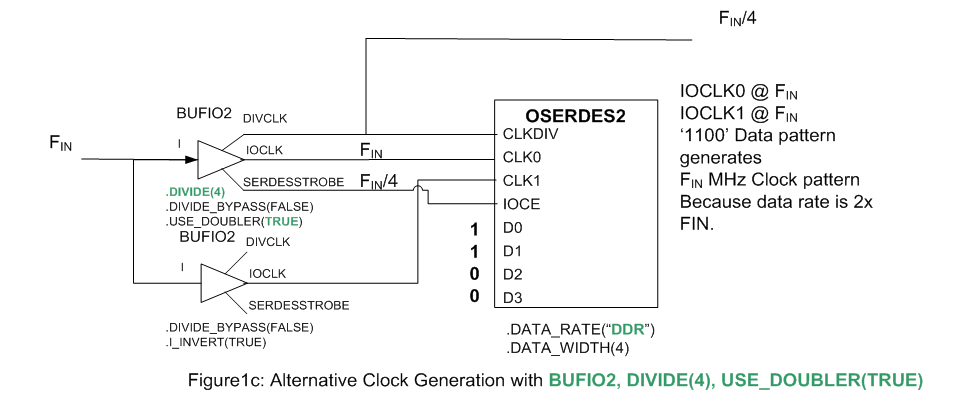

对于正在使用分频时钟来创建外部时钟输出的客户来说完全可以使用 OSERDES 方案,原因是DIVIDE(4) 的使用方法已在(图 1b)“通过 BFUIO2、DIVIDE(4) 实现的时钟生成方法”中给出。请注意来自 BUFIO2 的 IOCLK 只能在相同的半组内部路由至 I/O。可能产生路由限制。

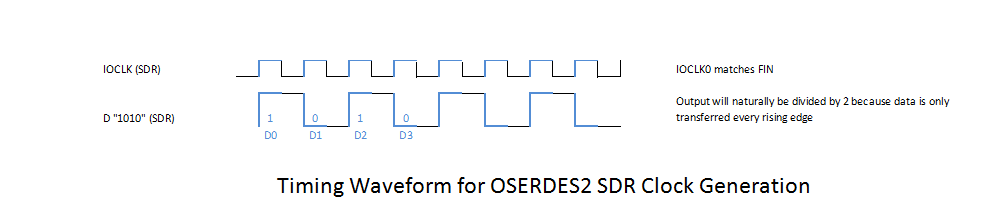

当使用 SDR 时,数据在 IOCLK (SDR) 的每个上升沿被送出,如“用 OSERDES2 SDR 生成时钟产生的时序波形”中所示。因此,驱动数据的形式为 1010 意味着数据极性在每个时钟沿 (IOCLK(SDR) 都会翻转。这代表时钟的数据速率模式将与 IOCLK 的频率相匹配。但是,我们的目的是生成 2 位的时钟数据模式(1 和 0),这意味着引脚的时钟模式将看似与 FIN/2 相同。

DataRate SDR_1010 = FIN

1/1/0/0 数据模式可生成具有一定数据速率的时钟脉冲,原因是这种时钟模式每隔两个数据位 (1,0) 就会重复出现。

FSDR_1010= DataRate SDR_1010 / 2 = FIN / 2

另外,对于想要使用 DDR 数据速率的客户而言还可以使用第二种 OSERDES2 方案,即为 OSERDES2 添加倍频器模式,如图 1c 所示。 可应用与 BUFIO2 相同的路由限制,但由于使用了 USE_DOUBLER(TRUE),因此需要注意一些附加的路由限制,特别是第二个 BUFIO2 (I_INVERT) 的要求。 依照 UG382 所述 BUFIO2 具有专用位置。此外,USE_DOUBLER(TRUE) 要求使用第二条路由线路(用于 BUFIO2_2CLK),这对于 GTP 时钟是不提供的。因此,这种方案只适用于从全局时钟引脚进行路由的情况。

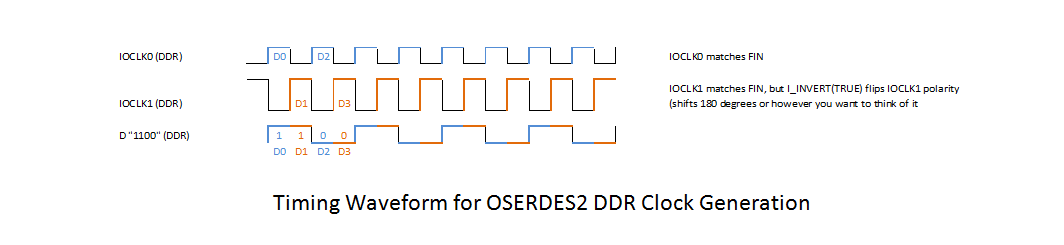

当使用 OSERDES2 with DATA_RATE (DDR) 时,请注意数据形式是不同的 (1100)。 这就是时钟生成方式的结果。现在驱动两个时钟,即CLK0 和 CLK1,如“OSERDES2 DDR 时钟生成的时序波形”中所示。 这种情况下,CLK0 每隔一位送出数据(例如对于 DIVIDE(4) 来说是 D0、D2)。 但由于使用了 DDR 模式,现在有第二个时钟源被第二个 BUFIO2 驱动,I_INVERT(TRUE) 驱动到 CLK1。 如图所示,IOCLK1 是反转的 IOCLK0(或者相位移动 180 度,假设是完美的 50/50 占空比),可用来建立第二个时钟。IOCLK1 也将送出间隔数据位,例如对于 DIVIDE(4) 来说是 D1, D3。

DataRate DDR_1100 = FIN * 2

数据模式 1/1/0/0 生成具有一定数据速率的时钟脉冲,因为它需要 4 个数据位 (1,1,0,0) 来建立一个时钟脉冲。

FDDR_1100 = DataRate DDR_1100 / 4 = FIN * 2 / 4 = FIN / 2

修订历史

05/22/13 - 初始版本

链接问答记录

主要问答记录

| Answer Number | 问答标题 | 问题版本 | 已解决问题的版本 |

|---|---|---|---|

| 34856 | Design Advisory Master Answer Record for Spartan-6 FPGA | N/A | N/A |

相关答复记录

| Answer Number | 问答标题 | 问题版本 | 已解决问题的版本 |

|---|---|---|---|

| 52296 | LogiCORE IP DisplayPort v3.2 - Is a DCM or PLL required to generate the RXUSRCLK2 for the Spartan-6 FPGA GTP? | N/A | N/A |

| 51964 | LogiCORE IP DisplayPort v3.2 - Clocking Structure for GTP 2-Byte Mode Interface | N/A | N/A |

| AR# 56113 | |

|---|---|

| 日期 | 01/19/2014 |

| 状态 | Active |

| Type | 设计咨询 |

| 器件 | |