Versal AI Core 系列

Versal AI Core 系列凭借集成型 AI 引擎实现了突破性 AI 推断和无线加速,与当今的服务器级 CPU 相比,可提供超过 100 倍的计算性能

拥有产品组合的最高计算能力,可实现最大的 AI 和工作负载加速

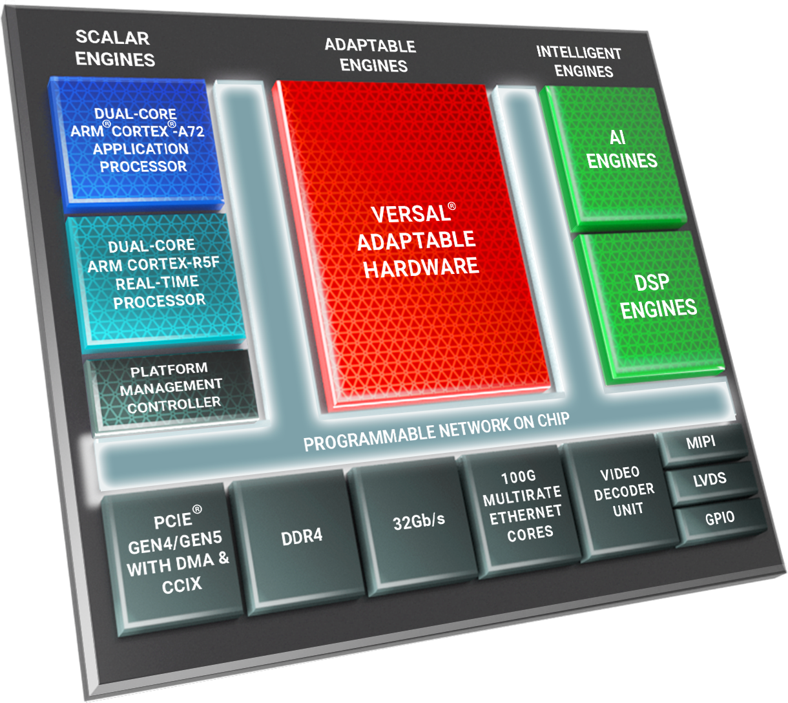

标量引擎

Versal™ ACAP 中提供了三种标量处理器类型,可支持各种应用需求。应用处理单元适合 OS 支持的复杂应用,而实时处理单元则完美适合需要低延迟、确定性和实时控制的应用。单独的平台管理控制器管理系统引导、安全性和调试。

自适应引擎

可编程逻辑可为不断变化的算法开发自定义计算模块。Versal ACAP 中重新排列的逻辑使每个 CLB 的密度提高 4 倍,从而减少了对昂贵全局路由的需求。自适应引擎装载了各类存储元件,并与可编程 I/O 紧密结合,使用户可为任意应用创建强大的加速器。

智能引擎

AI 引擎为基于矢量的算法提供高达 5 倍的更高计算密度。AI 引擎针对实时 DSP 和 AI / ML 计算进行了优化,可提供确定性的性能。

增强的 DSP 引擎为新操作和数据类型提供支持,包括单精度和半精度浮点以及复杂的 18x18 操作。

下一代 I/O

Versal AI Core 系列结合了PCIe® Gen4 合规性、CCIX 支持、高性能 GPIO 和支持各种以太网配置的多速率以太网 MAC,以最大程度地提升连接功能能和灵活性。此外,Versal AI Core 系列器件还具有重配置的低延迟 32.75Gb/s 收发器。

集成型 DDR 内存控制器

每个集成型 DDR 内存控制器提供高达 34.1GB/s 的带宽,并支持 DDR4 和 LPDDR4,同时还针对线性和随机流量进行了优化。这些集成的控制器与可编程的片上网络结合使用,消除了对可编程逻辑中软实现的需求,从而节省了开发时间和逻辑资源。

可编程的片上网络

可编程片上网络 (NoC) 在 Versal ACAP 架构中的不同计算引擎与集成 IP 模块之间提供了优化的多兆位互连,从而简化了时序收敛并节省了逻辑资源。NoC 编译器提供了简化的编程体验,同时允许用户管理延迟和 QoS,从而确保对关键数据路径进行优先级排序。

Versal™AI Core 系列器件针对计算密集型应用进行了优化,特别是数字信号处理、人工智能和机器学习

5G 无线电与波束形成

波束成形导致巨大的信号处理需求,这些需求需要实时处理。自适应引擎处理状态控制和数据格式化时,AI 引擎和 DSP 引擎正在处理定点和浮点信号处理工作负载,以实现高性能并行处理。

数据中心计算

随着卷积神经网络的不断发展,只有通过 Versal AI Core 系列器件才可解决不断增长的计算密度要求,Versal AI Core 系列器件的 AI 引擎经过优化,可有效地交付计算密度,既节省成本又节省能源。

面向智能城市的视频处理

Versal AI Core 系列器件可通过驱动实时车牌或面部识别的 AI 引擎、面向视频转码的 DSP 引擎以及面向视频缩放、压缩和自定义的自适应引擎来实现对智能城市的视频监控。

医疗图像处理

Versal AI Core 系列可加速并行波束形成和实时图像处理,以创建更高质量的图像和基于机器的图像分析,从而使医生和放射科医生能够更快、更准确地进行诊断。

雷达处理

将功能强大的、基于矢量的 DSP 引擎与较小尺寸的 AI 引擎相结合,可实现先进的雷达,例如有源电子扫描阵列。AI Core 系列器件在单个封装中提供每秒兆位的天线带宽。

无线测试设备

实时 DSP 被广泛用于无线通信测试设备中。Versal AI 引擎架构完美适合处理所有类型的协议实现,包括从数字前端到波束成形和基带的 5G。

Versal AI Core 系列功能简介

标量引擎功能

| VC1352 | VC1502 | VC1702 | VC1802 | VC1902 | VC2602 | VC2802 | |

|---|---|---|---|---|---|---|---|

| 应用处理单元 | 双核 Arm® Cortex -A72、48KB/32KB L1 高速缓存支持奇偶校验和 ECC,1MB L2 高速缓存支持 ECC | ||||||

| 实时处理单元 | 双核 Arm® Cortex -R5F、32KB/32KB L1 高速缓存以及支持 ECC 的 256KB TCM | ||||||

| 存储器 | 支持 ECC 的 256KB 片上内存 | ||||||

| 连接功能 | 以太网 (x2)、USB 2.0 (x1)、UART (x2)、SPI (x2)、I2C (x2)、CAN-FD (x2) | ||||||

智能引擎功能

| VC1352 | VC1502 | VC1702 | VC1802 | VC1902 | VC2602 | VC2802 | |

|---|---|---|---|---|---|---|---|

| AI 引擎 | 128 | 248 | 304 | 300 | 400 | 0 | 0 |

| AI 引擎-ML | 0 | 0 | 0 | 0 | 0 | 152 | 304 |

| DSP 引擎 | 928 | 1,312 | 1,312 | 1,600 | 1,968 | 984 | 1,312 |

灵活应变的引擎功能

| VC1352 | VC1502 | VC1702 | VC1802 | VC1902 | VC2602 | VC2802 | |

|---|---|---|---|---|---|---|---|

| 系统逻辑单元 | 540K | 797K | 981K | 1,586K | 1,968K | 820K | 1,139K |

| LUT 数 | 247K | 372K | 449K | 725K | 900K | 375K | 521K |

平台功能

| VC1352 | VC1502 | VC1702 | VC1802 | VC1902 | VC2602 | VC2802 | |

|---|---|---|---|---|---|---|---|

| NoC 主 / NoC 从端口 | 10 | 21 | 21 |

28 | 28 | 21 | 21 |

| DDR 内存控制器 | 2 | 3 | 3 |

4 | 4 | 3 | 3 |

| CCIX & PCIe® (带有 DMA) (CPM) | - | 1 x Gen4x16, CCIX |

1 x Gen4x16, CCIX |

1 x Gen4x16, CCIX |

1 x Gen4x16, CCIX |

2 x Gen5x8, CCIX |

2 x Gen5x8, CCIX |

| PCIe Express® | 1 x Gen4x8 | 4 x Gen4x8 | 4 x Gen4x8 | 4 x Gen4x8 | 4 x Gen4x8 | 4 x Gen5x4 | 4 x Gen5x4 |

| 100G Multirate Ethernet MAC | 1 | 3 | 4 | 4 | 4 | 2 | 2 |

| 视频解码器单元 (VDU) | - | - | - | - | - | 2 | 4 |

| 32.75Gb/s GTY 或 GTYP 收发器 | 8 | 32 | 44 |

44 | 44 | 32 | 32 |

技术文档

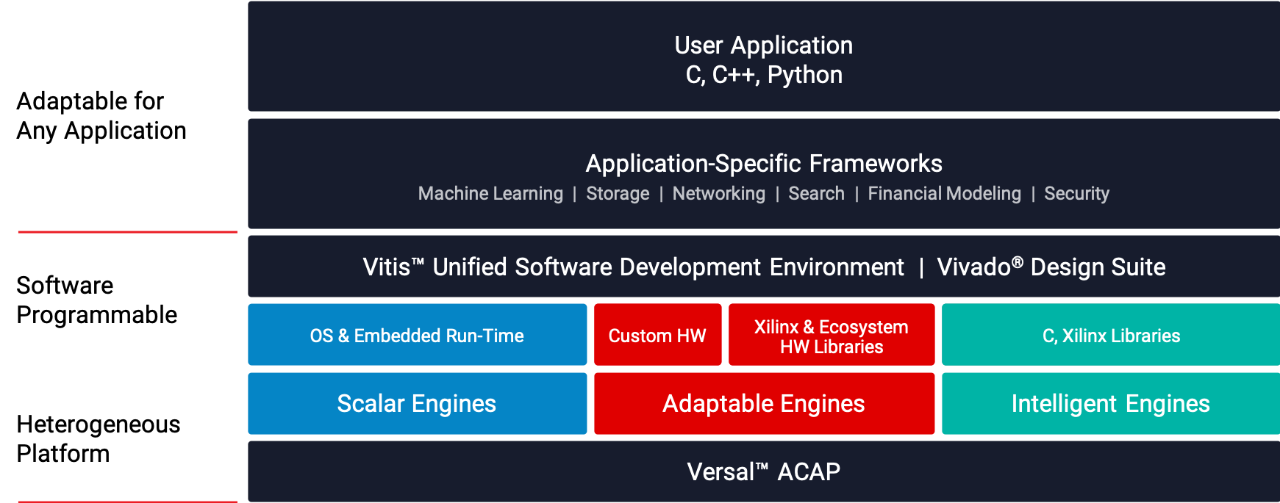

面向所有开发者的集成型软硬件平台

Versal™ ACAP 采用固有的软件可编程芯片基础架构,其设计自始至终都是以软件为导向的。增强型 Xilinx® Vivado® Design Suite 引入全新系统设计方法和开发环境,如流量分析仪、NoC 编译器和数据流建模等。一个紧密结合的高速、统一调试环境可加速跨灵活应变的标量智能引擎的调试与跟踪。

下载 Vivado Design Suite >

Xilinx Vitis™ 统一软件平台提供了全面的核开发套件,以及使用硬件加速技术的库。该平台提供从云端到边缘的高效、便捷、统一的软件环境。Vitis 统一软件平台是开源社区引以为傲的一份子,完全免费、开源。

下载 Vitis 统一软件平台 >

Versal ACAP 评估套件

欢迎率先体验 Versal ACAP 架构,从零开始构建,实现原生的软件可编程性。通过一系列工具、软件、库、IP、中间件和构架,ACAP 可通过业界标准设计流程实现各种定制化的加速计算解决方案。Versal AI Core 系列 VCK190 评估套件提供快速启动设计所需的一切。

培训课程

Xilinx 培训和学习资源提供了实用的实践技能和基础知识,可助力开发者在下一个开发项目中充分发挥生产力。

使用 Xilinx Versal ACAP 平台开启设计

使用 Versal ACAP 进行设计:架构和方法

使用 Versal ACAP 进行设计:可编程片上网络

使用 Versal ACAP 进行设计 - 电源和开发板设计

使用 Versal AI 引擎进行设计 1 :架构与设计流程

使用 Versal AI 引擎进行设计 2:使用 AI 引擎内核进行图形编程

重要视频

所有视频

重要视频

所有视频

Adaptable Advantage 博客

-

- MicroZed Chronicles: Bluespec RISC-V

- Oct 01, 2021

-

- MicroZed Chronicles: Certified Ubuntu on Xilinx SoCs

- Sep 24, 2021