AR# 34740

|MIG Virtex-6 DDR2/DDR3 - PHY Initialization and Calibration

描述

The PHY logic contains state logic for initializing the SDRAM memory after power-up and performs timing training of the read and write data paths to account for system static and dynamic delays.This section of the MIG Design Assistant focuses on the initialization and calibration (timing training) performed by the PHY at power-up.

The Virtex-6 Memory Interface Solutions User Guide (UG406)includes a detailed section on the PHY logic.Please review this material within the DDR2/DDR3 SDRAM Memory Interface Solution > Core Architecture >PHY section:

http://www.xilinx.com/support/documentation/ip_documentation/ug406.pdf

NOTE: This answer record is part of the Xilinx MIG Solution Center (Xilinx Answer 34243). The Xilinx MIG Solution Center is available to address all questions related to MIG. Whether you are starting a new design with MIG or troubleshooting a problem, use the MIG Solution Center to guide you to the right information.

解决方案

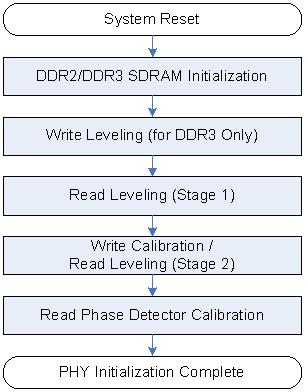

The following diagram shows the Virtex-6 PHY sequence for initialization and calibration:

When calibration completes successfully cal_done asserts. For detailed information on each stage, see the following:

- DDR2/DDR3 Initialization - (Xilinx Answer 34744)

- Write Leveling (DDR3 Only) - (Xilinx Answer 35094)

- Read Leveling Stage 1 - (Xilinx Answer 35118)

- CLKDIV Calibration Stage - (Xilinx Answer 37968)

- Read Leveling Stage 2 - (Xilinx Answer 35129)

- Write Calibration - (Xilinx Answer 35110)

- Read Phase Detector Calibration - (Xilinx Answer 35145) cal_done does not assert, an error occurred during calibration and requires further debugging. Please see the Calibration Debug section of this Virtex-6 MIG Design Assistant for further assistance: (Xilinx Answer 34743).

- The MIG Virtex-6 DDR2/DDR3 design does not support per-bit deskew. For further information, please see (Xilinx Answer 35163).

链接问答记录

主要问答记录

| Answer Number | 问答标题 | 问题版本 | 已解决问题的版本 |

|---|---|---|---|

| 35094 | MIG Virtex-6 and 7 Series DDR3 - Write Leveling | N/A | N/A |

子答复记录

| Answer Number | 问答标题 | 问题版本 | 已解决问题的版本 |

|---|---|---|---|

| 35163 | MIG 7 Series and Virtex-6 DDR2/DDR3 - Per-Bit Deskew | N/A | N/A |

相关答复记录

| Answer Number | 问答标题 | 问题版本 | 已解决问题的版本 |

|---|---|---|---|

| 37968 | MIG Virtex-6 DDR2/DDR3 - Additional Calibration Stage (CLKDIV Calibration Stage) Added To Calibrate the Timing of the BUFIO to BUFR Transfer | N/A | N/A |

| 35129 | MIG Virtex-6 DDR2/DDR3 - Read Leveling Stage 2 | N/A | N/A |

| 35118 | MIG Virtex-6 DDR2/DDR3 - Read Leveling Stage 1 | N/A | N/A |

| 35110 | MIG Virtex-6 DDR3 - Write Calibration | N/A | N/A |

| 34744 | MIG 7 Series and Virtex-6 DDR2/DDR3 - PHY DDR2/DDR3 Initialization | N/A | N/A |

| 34718 | MIG Virtex-6 DDR2/DDR3 - PHY Architecture | N/A | N/A |

| 34480 | MIG Virtex-6 DDR2/DDR3 - Phase Detection Circuit and Periodic Reads | N/A | N/A |

| 34743 | MIG Virtex-6 DDR2/DDR3 - Debugging Calibration Failures | N/A | N/A |