AR# 35818

|Design Advisory for Spartan-6 FPGA - Memory Controller Block (MCB) Performance Change for DDR2 Interfaces

描述

The Spartan-6 FPGA Memory Controller Block (MCB) has new data rate specifications and performance modes for DDR2 interfaces as specified in the Spartan-6 FPGA Data Sheet v1.5(DS162): http://www.xilinx.com/support/documentation/data_sheets/ds162.pdf.

NOTE: These data rate changes do not apply to DDR3 interfaces.For full details, see (Xilinx Answer 41520).

解决方案

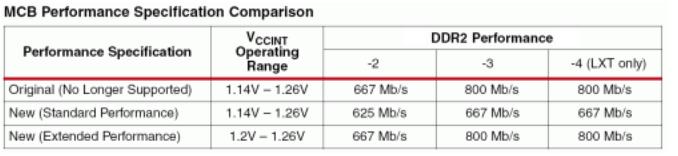

The Spartan-6 FPGA MCB performance was changed inJune 2010.When operating the MCB in the Standard Performance mode over the full VCCINT operating range, the DDR2 maximum data rate specifications are reduced. A new Extended Performance mode was also added to enable operation of DDR2 interfaces at the original data rate specifications by using a tighter VCCINT range. The following table details the new performance specifications and modes.DDR3, DDR and LPDDR (Mobile DDR) performance is unchanged.

This change applies to all Spartan-6 devices.The production errata (EN148) and PCN notification (XCN10024) for the LX16 and LX45 devices already in production include this change.

There are some exceptions to the list of affected devices:

- The devices in production before this change still meet the original specifications. This includes the LX16 and LX45 -2C with JTAG ID Revision Code 2; see thePCN notification(XCN10024). These devices are no longer available and cannot be special ordered; therefore, designs should be updated to match the new specifications.

- The Lower Power Spartan-6 -1L devices have not been specified yet and therefore their performance does not change.

- The LX4 and the devices in the TQG144 and CPG196 do not support the MCBs and therefore are not affected.

Work-around

For designs that were planning totarget a frequencyfor a certain speed grade which is now in the Extended Performance mode, two options are available:

- Move up a speed grade.

- Change VCCINT to the Extended Performancemode of 1.20V to 1.26V.

A VCCINT range of 1.20V to 1.26V is 1.23V +/- 2.5%. Various regulators support this operating range. The 1.23V nominal VCCINT results in a higher nominal ICCINT; see (Xilinx Answer 35866).

Software Support

The ISE 12.1 software reflects the original timing specifications. When using the MIG/MPMC tools, make sure a valid performance limit is specified for the interface according to the speed grade and VCCINT range that is being used.

The ISE 12.2 software in July 2010 reflects the new timing specifications both in the MIG/MPMC selections and in the speed file.A CONFIG constraint is available to specify whether the VCCINT will use the 1.14V-1.26V range, with theStandard MCB performance, or the 1.20V-1.26V range, with theExtended MCB performance.This constraint is automatically inserted into the UCF file based on the selection made in the MIG GUI delivered with ISE 12.2 software. MPMC users need to manually add the constraint to the UCF.

The new constraint, to be used with the ISE 12.2 and later software:

CONFIG MCB_PERFORMANCE = STANDARD| EXTENDED

Differentiating Devices Tested to Original and New Specifications

The devices tested to the original specifications are limited to the LX16 and LX45 -2C devices.They are differentiated by the JTAG ID Revision Code of "2". The LX16 and LX45 -2C devices with a JTAG ID Revision Code of "3" are the devices tested to the new specifications.The mask revision code is the same for both.The devices tested to the original specification are no longer available and cannot be directly ordered as such.

All other Spartan-6 devices are characterized to the new specifications listed in the table above, and the Spartan-6FPGAData Sheet (DS162):

http://www.xilinx.com/support/documentation/data_sheets/ds162.pdf.

Other References

To see a list of other recent and important MCB Answer Records, refer to:

(Xilinx Answer 33566) Design Advisories for MIG including DDR3, DDR2, DDR, Spartan-6 FPGA MCB, RPDRAMII, QDRII+, QDRII, DDRII cores

(Xilinx Answer 34587) MIG v3.4 - Release Notes and Known Issues for ISE Design Suite 12.1

(Xilinx Answer 34609) 12.x EDK - Master Answer Record List

链接问答记录

主要问答记录

| Answer Number | 问答标题 | 问题版本 | 已解决问题的版本 |

|---|---|---|---|

| 33566 | Design Advisory Master Answer Record for Programmable Logic Based External Memory Interface Solutions for Virtex-6, Spartan-6, all 7 Series Devices, and all UltraScale based Devices | N/A | N/A |

| 34856 | Design Advisory Master Answer Record for Spartan-6 FPGA | N/A | N/A |

| 35180 | Spartan-6 - 12.4 Software Known Issues related to the Spartan-6 FPGA | N/A | N/A |

相关答复记录

| Answer Number | 问答标题 | 问题版本 | 已解决问题的版本 |

|---|---|---|---|

| 37498 | MIG Design Assistant - Spartan-6 Core Functionality | N/A | N/A |

| 35866 | Spartan-6 - Extended Performance Mode VCCINT Max Quiescent values | N/A | N/A |

| 42024 | MIG 7 系列 DDR3 – FPGA 和 DDR3 SDRAM 之间的推荐迹线阻抗是什么? | N/A | N/A |

| 33566 | Design Advisory Master Answer Record for Programmable Logic Based External Memory Interface Solutions for Virtex-6, Spartan-6, all 7 Series Devices, and all UltraScale based Devices | N/A | N/A |

| AR# 35818 | |

|---|---|

| 日期 | 11/15/2012 |

| 状态 | Active |

| Type | 设计咨询 |

| 器件 | |

| Tools | |

| IP | |